实验二 按键控制数码管(消抖)

代码

//Name: key_xiaodou.v

//Function:

// PIN_27 50MHz SW8 KEY8 hgfedcba select

// clk rst key seg8[7:0] bit8[7:0]

//Author: YanceyLu

module key_xiaodou(clk,rst,key,seg8,bit8);

input clk,rst,key;

output [7:0] seg8;

output [7:0] bit8;

key_delay_xiaodou key_delay(clk,rst,key,okey);

reg [7:0] seg8;

reg [3:0] cnt;

assign bit8=8'b11111110;

always @(posedge clk or negedge rst)

begin

if(!rst)

cnt<=0;

else if(!okey)

begin

if(cnt==9)

cnt<=0;

else

cnt<=cnt+1;

end

else

cnt<=cnt;

end

always @(cnt)

begin

case(cnt)

0: seg8<=8'hc0;//0

1: seg8<=8'hf9;//1

2: seg8<=8'ha4;//2

3: seg8<=8'hb0;//3

4: seg8<=8'h99;//4

5: seg8<=8'h92;//5

6: seg8<=8'h82;//6

7: seg8<=8'hf8;//7

8: seg8<=8'h80;//8

9: seg8<=8'h90;//9

endcase

end

endmodule

//Name: key_delay_xiaodou.v

//Function:

// push key: 0

// pop key: 1

// xiao dou,using delay.

//Author: YanceyLu

module key_delay_xiaodou(clk,rst,i_pulse,o_pulse);

input clk,rst,i_pulse;

output o_pulse;

reg [19:0] delay_cnt;

reg [1:0] pulse_reg;

reg [1:0] pulse_reg_new;

wire low;

wire low_new;

//Test falling edge

always @(posedge clk or negedge rst)

begin

if(!rst)

pulse_reg[0]<=1;

else

pulse_reg[0]<=i_pulse;

end

always @(posedge clk or negedge rst)

begin

if(!rst)

pulse_reg[1]<=1;

else

pulse_reg[1]<=pulse_reg[0];

end

assign low=pulse_reg[1]&(~pulse_reg[0]);

//Delay 20ms

always @(posedge clk or negedge rst)

begin

if(!rst)

delay_cnt<=0;

else if(low)

delay_cnt<=0;

else

delay_cnt<=delay_cnt+1;

end

//Test falling edge again

always @(posedge clk or negedge rst)

begin

if(!rst)

pulse_reg_new[0]<=1;

else if(delay_cnt==20'hfffff)

pulse_reg_new[0]<=i_pulse;

end

always @(posedge clk or negedge rst)

begin

if(!rst)

pulse_reg_new[1]<=1;

else

pulse_reg_new[1]<=pulse_reg_new[0];

end

assign low_new=pulse_reg_new[1]&(~pulse_reg_new[0]);

//Output

assign o_pulse=~low_new;

endmodule

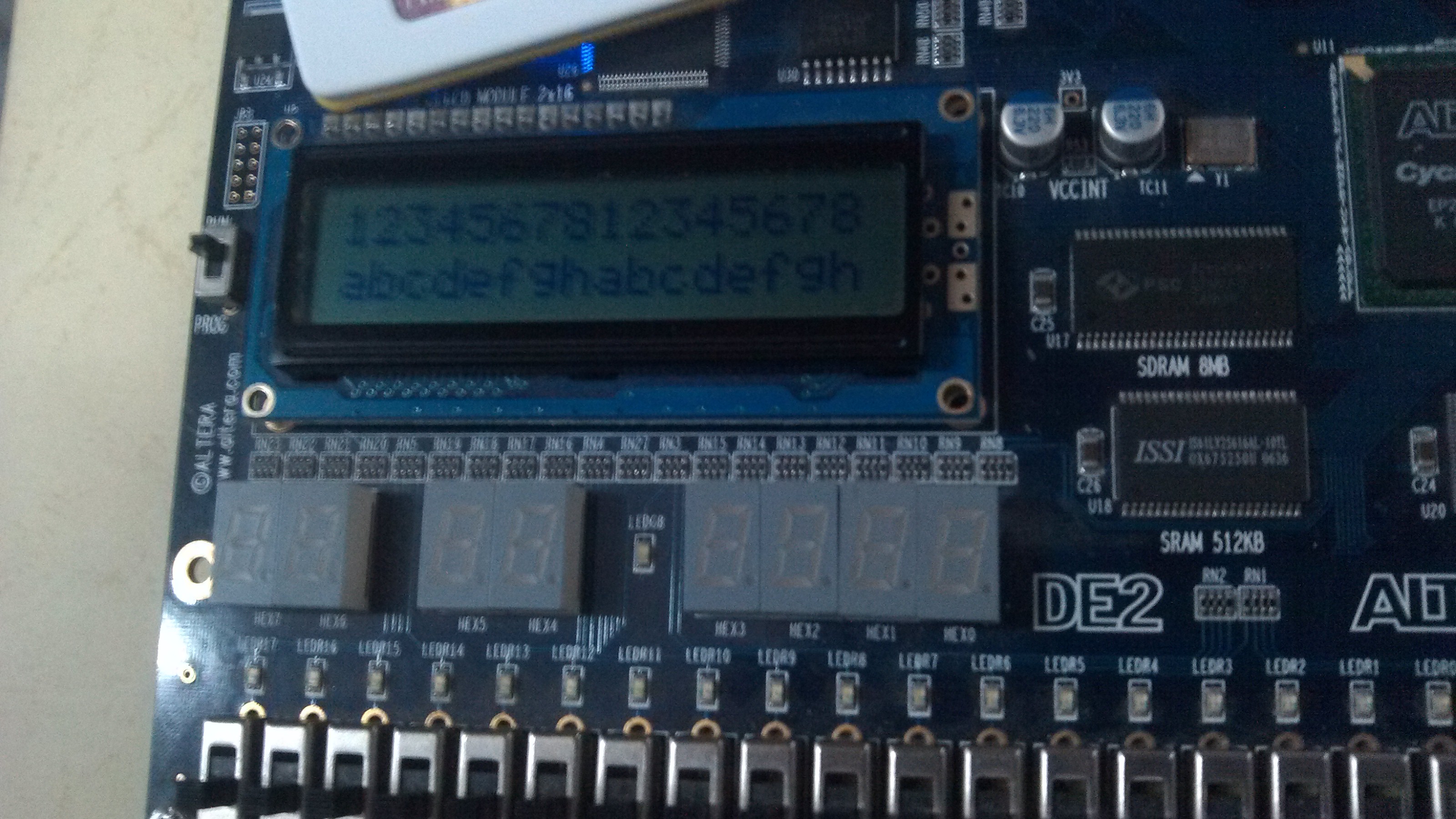

视频效果

我要赚赏金

我要赚赏金