共阳数码管,说白了也是延时和IO反转。

只不过在VerilogHDL里边,用到了不少新东西。比如assign语句和case语句。

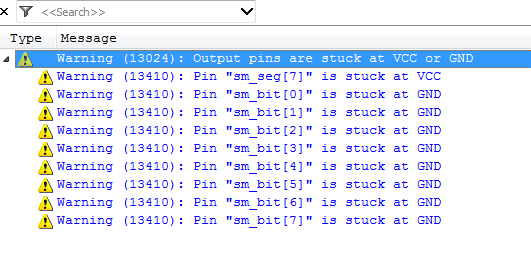

这个例子,在编译的时候有个警告信息:

Warning (13024): Output pins are stuck at VCC or GND

就是说,输出引脚连到了VCC或者连到了GND。不知道为什么会有这种警告?引脚分配应该没问题的。照着原理图分配引脚的。

为什么会有这样的警告?

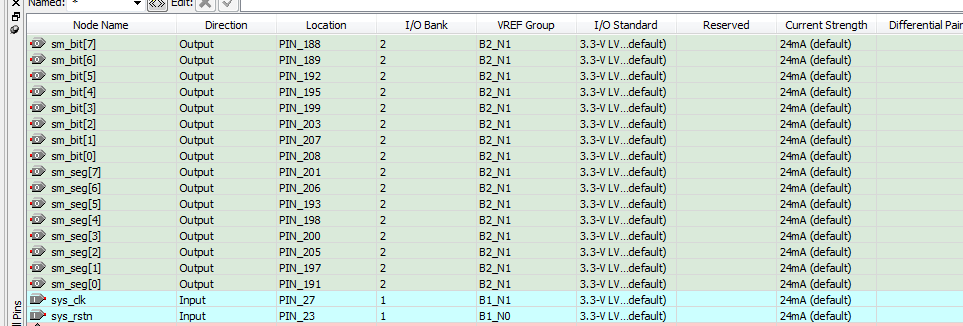

警告信息和引脚分配见下图:

这几个警告没问题的,警告的意思是有引脚一直处于高电平或是低电平。在该设计中,若要数码管静态显示,则位选信号要置低。

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| Chaos-nano:专为低资源单片机设计的轻量级协作式异步操作系统(ATMEGA328P轻量级操作系统)—— 详细介绍被打赏¥16元 | |

| FPGA配置被打赏¥10元 | |

| Chaos-nano协作式异步操作系统:赋能MicrochipAVR8位单片机的革新之路被打赏¥15元 | |

| 基于esp32开发时串口工具的注意点被打赏¥24元 | |

| 基于FireBeetle2ESP32-C5开发板的舵机控制被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板制作的电子相册被打赏¥32元 | |

| 基于FireBeetle2ESP32-C5开发板的超声波测距及显示被打赏¥21元 | |

| FireBeetle2ESP32-C5上RTC电子时钟的实现被打赏¥25元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板读取SD卡被打赏¥23元 | |

| 【S32K3XX】Standby RAM 重启后数据异常问题调查被打赏¥38元 | |