共阳数码管,说白了也是延时和IO反转。

只不过在VerilogHDL里边,用到了不少新东西。比如assign语句和case语句。

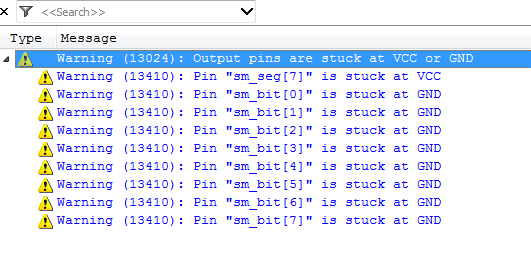

这个例子,在编译的时候有个警告信息:

Warning (13024): Output pins are stuck at VCC or GND

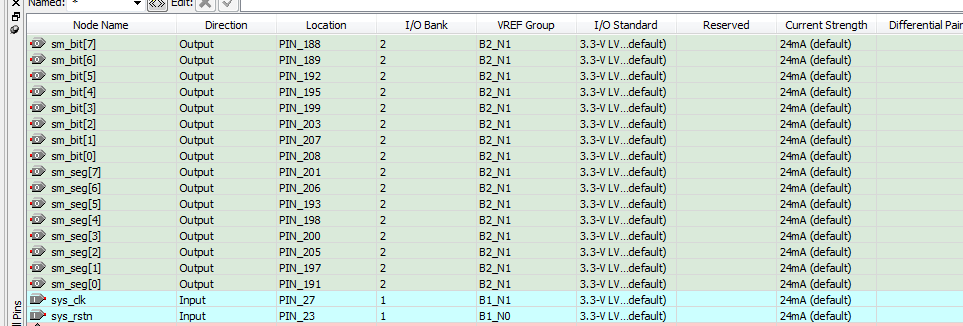

就是说,输出引脚连到了VCC或者连到了GND。不知道为什么会有这种警告?引脚分配应该没问题的。照着原理图分配引脚的。

为什么会有这样的警告?

警告信息和引脚分配见下图:

这几个警告没问题的,警告的意思是有引脚一直处于高电平或是低电平。在该设计中,若要数码管静态显示,则位选信号要置低。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |