作者:湖北师范学院信工学院 谢虎城 刘蕾 周密

指导教师:梁赫西 闻辉

作品简介

开发背景:

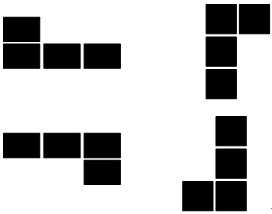

俄罗斯方块作为家喻户晓老少皆宜的大众游戏,具有的数学性、动态性与知名度。其上手极其简单,但是要熟练地掌握其中的操作与摆放技巧,难度却不低。本次ITAT电子系统设计团体赛,我们小组制作的是一款基于basys2开发板的俄罗斯方块(tetris)的游戏。

结构说明:

显示器技术规格提供的行频一般在30kHz~45kHz(保守数据),场频一般在50Hz~75Hz,针对以上数据,30kHz的行频进行扫描时所需时钟频率为:30kHz×800(行周期)=24MHz,则场频为:30kHz÷525(场周期)=57.14Hz 。

本方块游戏采用标准的VGA(640×480,60Hz),主频为50MHz,VGA工作频率为25MHz。,本设计在原开发板的基础上增添了一片50M的有源晶振,以稳定VGA显示器的显示。

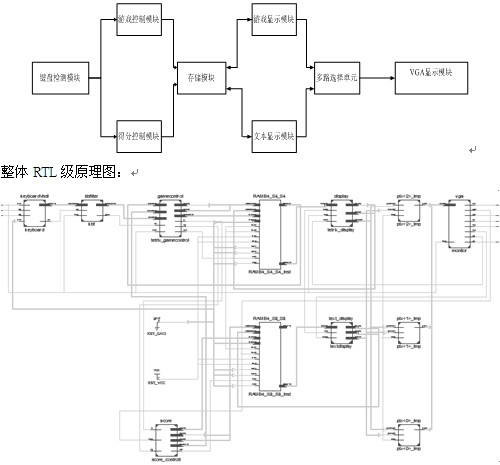

软件平台上,本小组,利用Xlinx公司的ise14平台及 VHDL语言,分别设计了键盘检测模块、得分控制模块、游戏控制模块、存储模块(两块BRAM,分别存储图像颜色及字符编码)、文本显示模块、游戏显示模块、以及VGA显示模块,最后对各个模块进行了接口建模,组成了该tetris设计。

功能与使用说明:

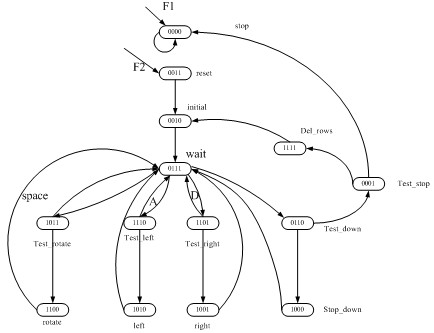

(1) 游戏开始、复位按键F2

开始时游戏处于停止状态须按下按键F2开始新游戏,游戏过程中也可以通 过按键F2随时重新开始游戏

(2)游戏暂停及继续游戏按键F1

游戏过程中可通过按键A、D控制左、右移动方块,按键S按下,以x4速度加速下降,按键Space可控制旋转方块,游戏途中可通过按键F1暂停游戏,须开始时再次按下按键F1即可。

(3) 游戏得分统计

在游戏模块右边的提示栏,可显示基本操作及当前得分数,每消除一行可得分1分,最高得分为9999分。

(4) 游戏最高分统计

游戏提示栏在每次重新开始游戏时可记录本次游戏的分数,若超过最高分则被统计显示。

(5) 得分加速

游戏进行过程中,默认以x1速度下降;得分超过100分,速度加倍为x2模式;超过200分,速度加倍为x3模式;超过300分,速度加倍为x4模式。

平台选型说明

基于basys2开发板的设计平台,外接一个50M有源晶振。

设计说明

一、设计原理

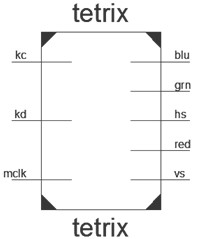

KC :PS/2时钟输入

KD :PS/2数据输入

MCLK:系统50M有源晶振输入

BLU:vga接口的蓝色输出信号

GRN:vga接口的绿色输出信号

HS :vga接口的行同步信号

RED:vga接口的红色输出信号

VS :vga接口的列同步信号

通过检测键盘上的F1、F2、A、S、D、以及空格键控制游戏的暂停/继续、重新开始、模块左移、模块最快速度(X4)下降、模块右移、逆时钟方向旋转。游戏过程中可以随时通过F1暂停开始游戏,以及随时通过F2重新开始游戏,每次结束游戏重新开始时系统将记录下游戏最高分。得分在100下以X1速度下降,100-200以X2速度下降,200-300以X3速度下降,300分以上以X4速度下降

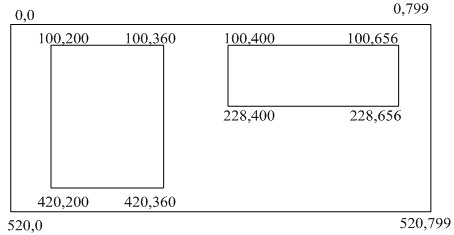

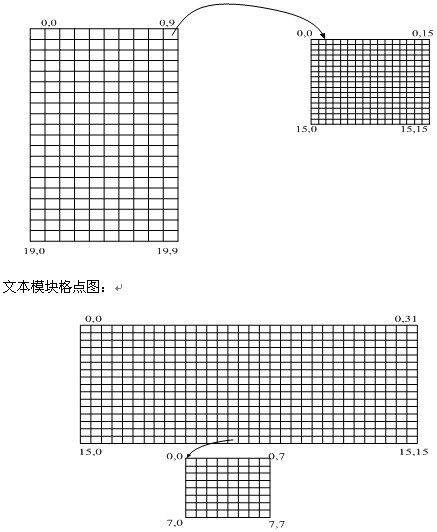

在整体上,取屏幕521*800个像素点,取20*10*16*16个像素点作为游戏区域,取16*32*8*8个像素点作为文本显示区域。设计图如下:

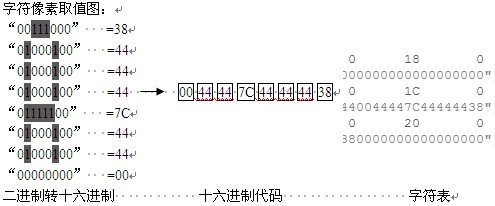

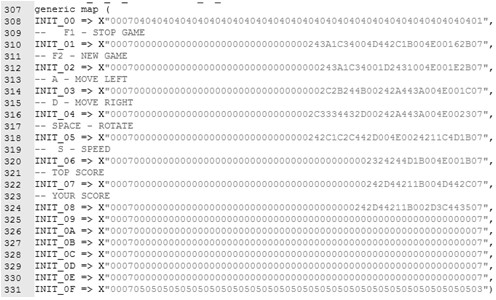

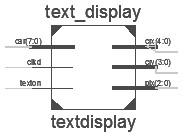

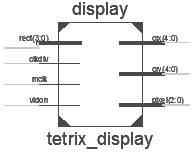

tetris游戏主要包括键盘检测模块、得分控制模块、游戏控制模块、存储模块(两块BRAM,分别存储图像颜色及字符编码)、文本显示模块、游戏显示模块、以及VGA显示模块。原理图如下:

二、设计方案

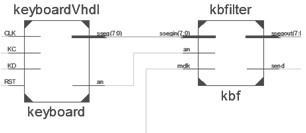

1 、键盘检测模块设计

CLK :主时钟输入

KC :PS/2键盘时钟

KD :PS/2键盘数据

RST :异步复位

AN :按键确认

SSEG(7:0):按键采样数据

SSEGOUT(7:0):处理后按键数据

SEND:输出信号

该模块采用边沿检测法,通过两片Flip Flops构成移位寄存器,同时对键盘时钟及数据进行存储,并通过计数器控制接收的位数,然后截取其中有效的数据,送往下一模块进行检测,判断通码或断码,取断码的后八位数据。

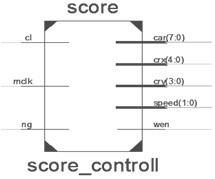

2、得分控制模块设计

CL :计数信号

MCLK :主时钟输入

NG :新游戏信号

CAR(7:0) :BRAM文本数据输出

CRX(4:0) :BRAM地址输出

CRY(3:0) :BRAM地址输出

SPEED(1:0) :游戏速度输出

WEN :BRAM写使能

此模块接收来自游戏控制模块的复位和计数信号,新游戏开始时,检测得分数据是否大于最大值。比较结果用于判定是否需要更新最高得分的记录数据。不为最高值,则直接分数清零,进入游戏开始状态。在修改分数值的时候,仅修改字符对应BRAM的映射表,由文本显示模块负责寻址读取数据。同时在该模块,通过得分的记录信息,从而设置了多路选择,通过分值的不同输出不同的速度状态,传递至游戏控制模块

3、游戏控制模块设计

RECTIN(3:0) :BRAM数据输入

SPEED(1:0) :游戏速度信号

SSEG(7:0) :键盘通码

AN :按键确认信号

MCLK :主时钟输入

CRX(4:0) :BRAM地址输出

CRY(4:0) : BRAM地址输出

RECTOUT(1:0) : BRAM数据输出

CL :计数信号

NG :新游戏开始信号

WEN :BRAM写使能

我要赚赏金

我要赚赏金