根据您提供的信息,我们可以构建关于多输出门(缓冲门buf和非门not)的实例说明以及它们的真值表。

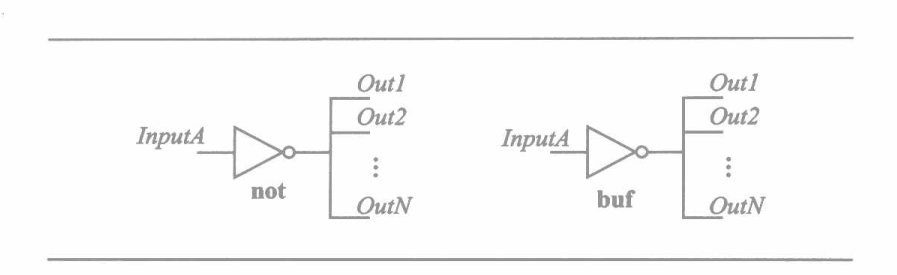

多输出门只有单个输入,有单个或多个输出端,又可称之为 buffer,起缓冲、延时作用。

示例一:

buf(缓冲器) not(非门)

示例二:

multiple_output_gate_type [instance_name (Out1,Out2,...0utN,InputA);

和多输入门类似,可以使用模块例化的方式对多输出门进行调用。

门级单元第一个端口是输出,最后一个端口是输入。当输出端口超过 1 个时,需将输出信号在最后一个输入端口前排列。

例化时也可以不指定实例的名字。

//buf buf buf1 (OUTX2, IN1) ; //2 output buf buf2 (OUTY2, OUTY3, IN2) ; //no instantiation name not (OUTZ3, IN3) ;

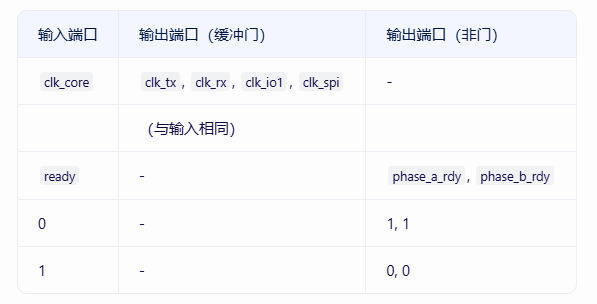

缓冲门(Buffer Gate)实例

buf u5buf(clk_tx, clk_rx, clk_io1, clk_spi, clk_core);

在这个实例中,u5buf是缓冲门的一个实例名。它有一个输入端口clk_core和四个输出端口:clk_tx、clk_rx、clk_io1和clk_spi。缓冲门的功能是将输入信号直接传输到所有输出端口,而不进行任何逻辑变换。

非门(NOT Gate)实例

not u8not(phase_a_rdy, phase_b_rdy, ready);

在这个实例中,u8not是非门的一个实例名。它有一个输入端口ready和两个输出端口:phase_a_rdy和phase_b_rdy。非门的功能是将输入信号进行逻辑取反,然后将取反后的信号传输到所有输出端口。

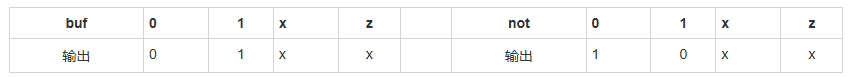

真值表

多输出门的真值表:

a)buf门的真值

(b)not门的真值

总结:

多输出门,缓冲门(buf)和非门(not),具有单个输入和多个输出端口。缓冲门直接传输输入信号至所有输出,无逻辑变换;

非门则对输入信号取反后传输至输出。在实例化时,可指定实例名及输入输出端口,输出端口列于输入端口前。

缓冲门实例u5buf将输入clk_core的信号直接传输至四个输出端口。

非门实例u8not对输入ready的信号取反后,传输至两个输出端口。

真值表展示了这些门的逻辑行为,对于理解和设计电路至关重要。多输出门在电路设计中扮演重要角色,提供信号缓冲和逻辑变换功能。

我要赚赏金

我要赚赏金