在大功率PCB设计中,对电压需求的管理是确保安全性和可靠性的首要任务。疏忽电压隔离不仅会导致电路板故障,还可能引发短路、电弧,甚至对操作人员构成严重威胁。本文将深入探讨如何识别和实施 PCB 的电压隔离需求。

1. 尽早识别隔离需求在设计过程的最初阶段就必须明确电压隔离需求。这包括:

最大工作电压:您的设计将承受的最高电压是多少?是28V、270V还是1000V?

应用特定标准:设计是否需要遵守特定的行业标准?例如:

IEC 62368-1(音视频及IT设备)

IEC 60601(医疗设备)

NASA-STD-4005A(低地球轨道航天器充电)

安全边界:是否需要为操作员安全设置隔离边界?

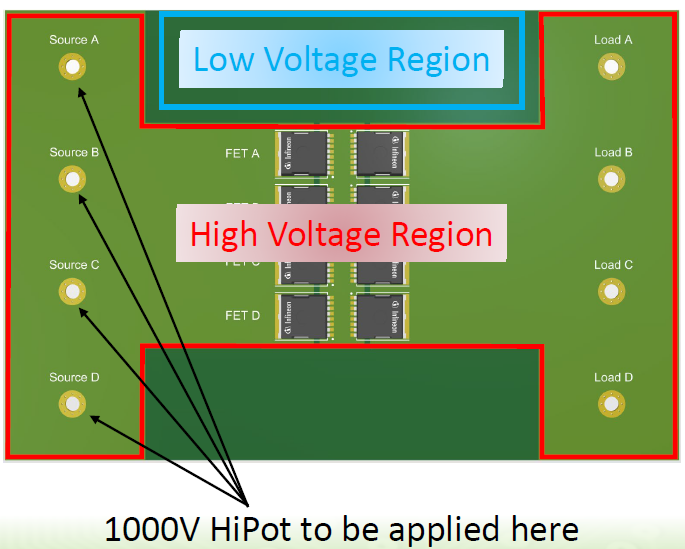

HiPot 测试:硬件是否需要进行高压测试?测试电压是多少?

这些需求将直接影响您的布局规划、可用布线面积和元件选择。

2. 理解IPC-2221标准当没有特定的应用标准时,IPC-2221(通用印制电路板设计标准)是我们的黄金准则。该标准根据电压水平和设备类型来规定最小导体间距。

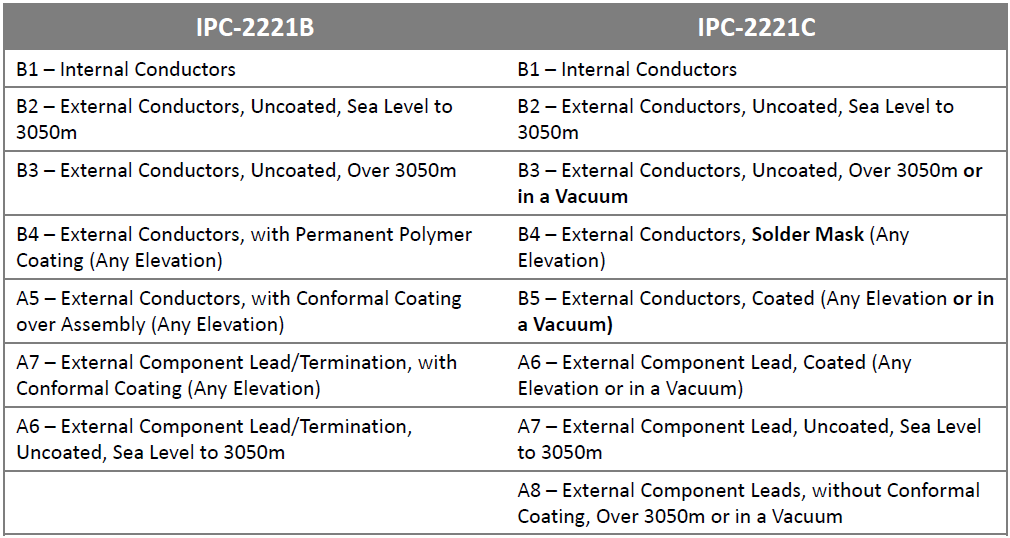

IPC-2221将导体分为不同类型,例如:

B1:内部导体

B4:带有永久聚合物涂层(如阻焊层)的外部导体

A6:未涂覆的外部元件引线/端子

A7:带有保形涂层(Conformal Coating)的外部元件引线/端子

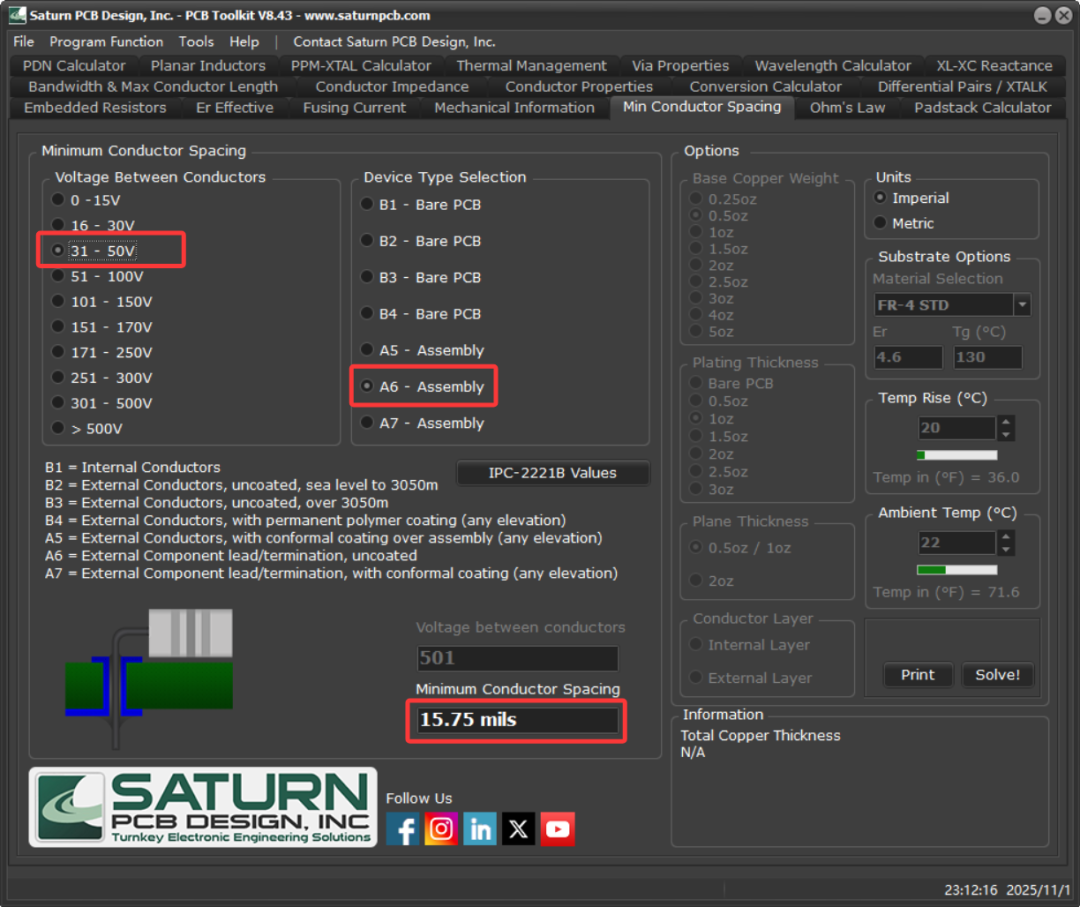

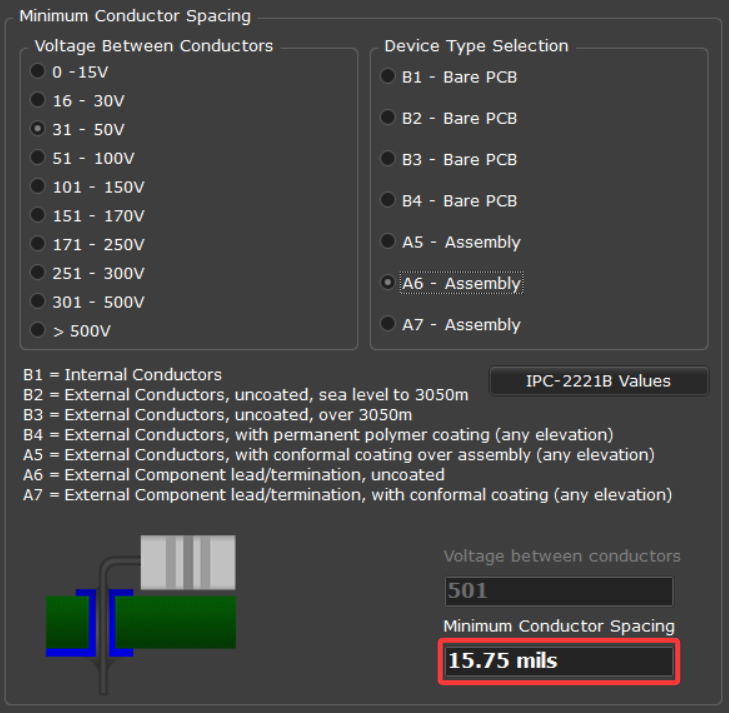

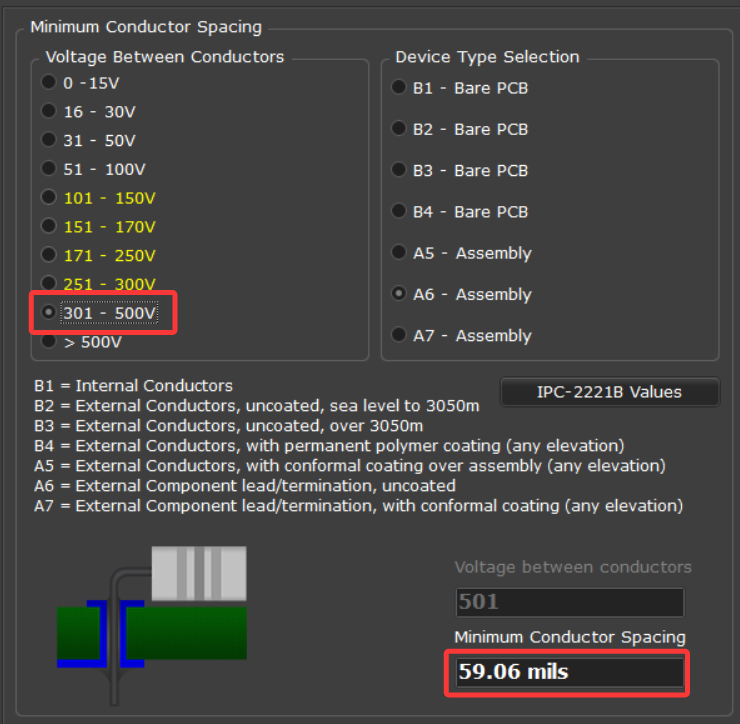

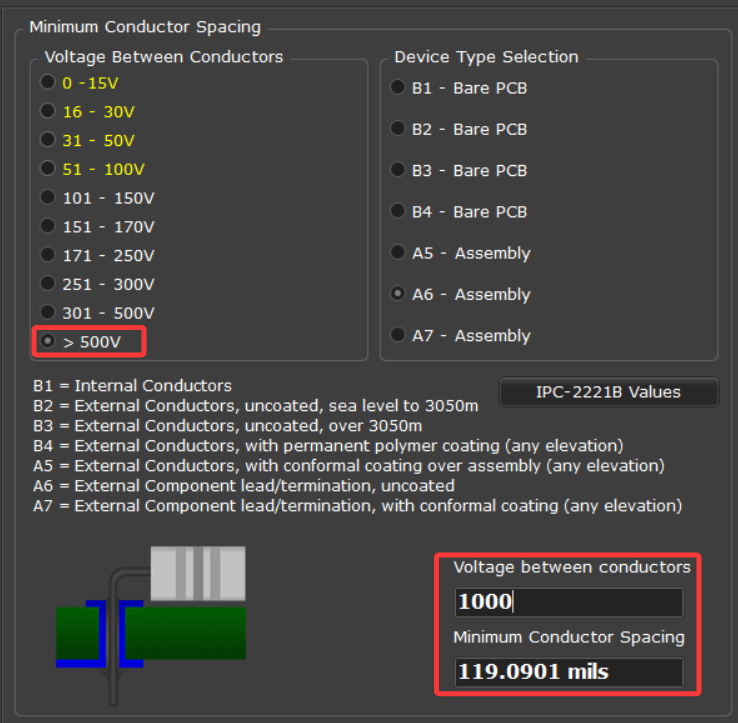

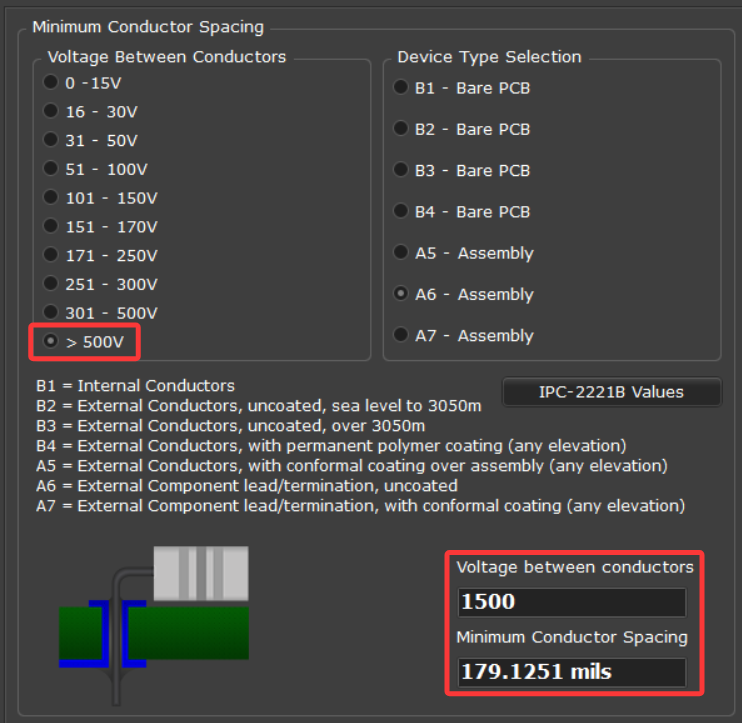

目前大部分的计算器仍使用 IPC-2221 Rev B,比如打开 Saturn PCB Tools,切换到 “最小导体间距” 标签,可以看到支持 7 种器件类型。下图展示了导体间电压为 31-50V,器件类型为 A6 时,最小间距要求为 15.75 mil。

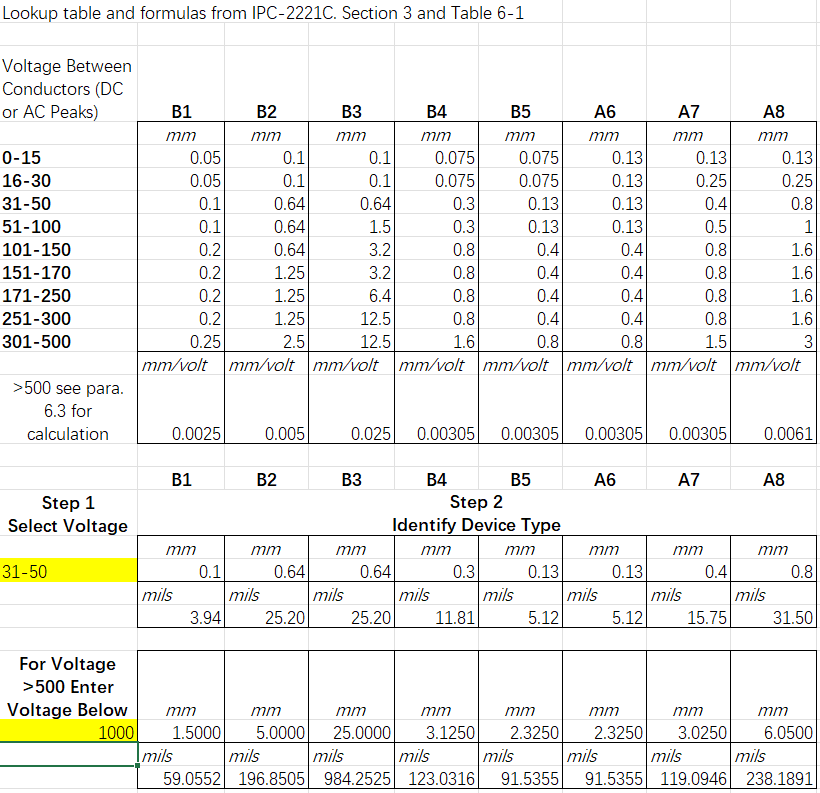

IPC-2221标准在C版本(2003年12月发布)中进行了更新,调整了间距值并增加了 A8 设备类型。下表为 2221 C 的查找表。

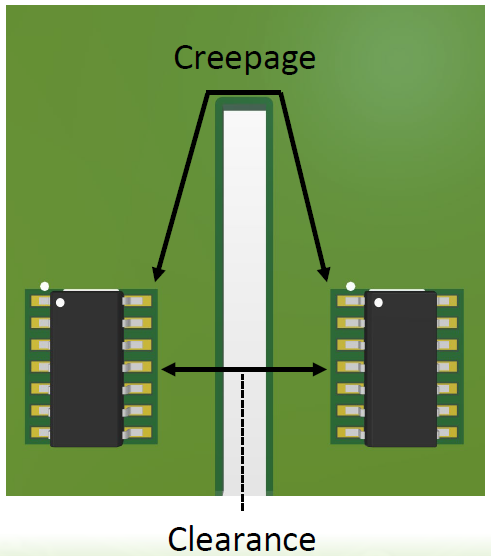

在讨论隔离时,必须区分两个关键概念:

电气间隙 (Clearance):两导体之间通过空气的最短直线距离。这主要受空气中颗粒物的影响。

爬电距离 (Creepage):两导体之间沿绝缘表面的最短距离。这受表面污染、湿气和残留物积聚的影响。

应用标准通常会根据预期的环境污染等级来定义所需的爬电距离和电气间隙。

明确需求后,必须在布局中严格执行:

划分电压区域:在布局中明确划分高压区和低压区。

执行设计规则:在EDA工具中设置严格的间隙和爬电距离规则,不要依赖手动检查。

跨边界元件:任何跨越隔离边界的元件(如光耦、变压器)本身必须具有足够的隔离等级。

高压额定值的元件并不意味着在您的设计中就能实现该额定值。封装和焊盘布局往往是真正的限制因素。

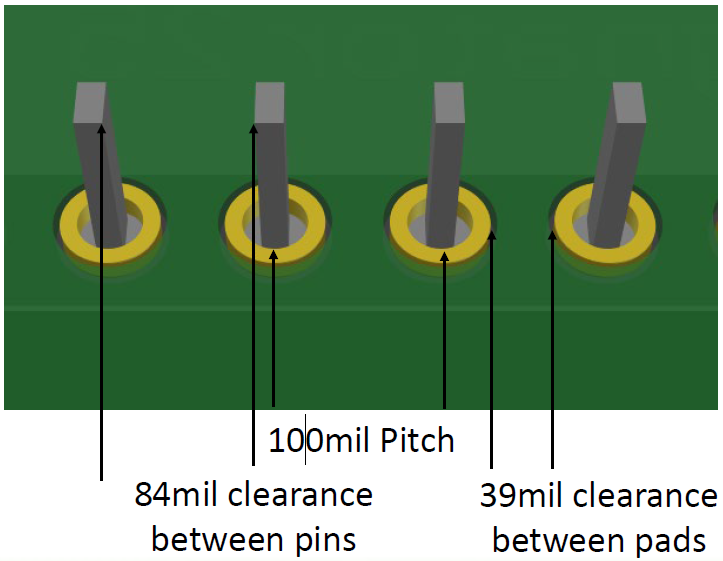

通孔器件 (THT):必须同时检查元件引脚之间(例如,100mil间距的连接器)和PCB焊盘之间的间隙。在某些情况下,焊盘间的距离(例如39mil)可能成为瓶颈,将设计的电压上限从720V拉低到300V。

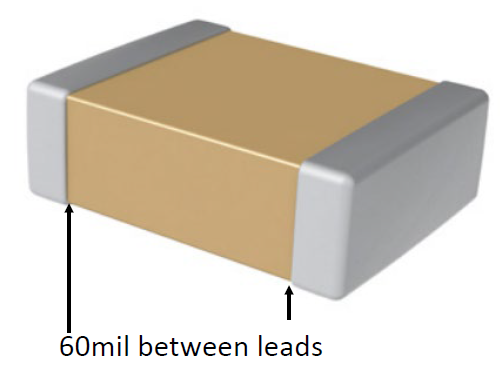

表贴器件 (SMD):同样,一个额定2000V的0805电容,其端子间的物理距离(例如60mil)可能根据IPC-2221标准(如A6类型)将其在应用中的最大电压限制在720V。

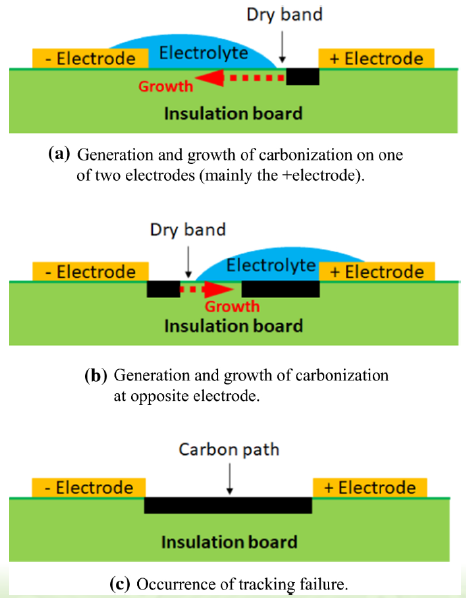

CTI (Comparative Tracking Index)是衡量绝缘材料在暴露于污染时抵抗电压击穿能力的指标。

测试方法:在材料表面施加电压,并滴加电解液,观察材料何时开始碳化(即“漏电起痕”)。

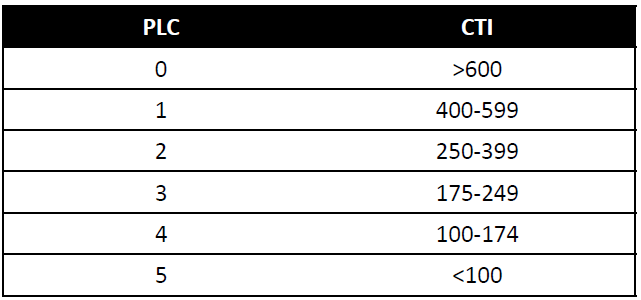

PLC等级:CTI值被分为0到5的性能等级(PLC)。PLC 0代表最佳性能(>600V)。

选材标准:IPC-2221的默认间距值基于CTI为175(PLC 3)的材料。如果您的工作电压高于175V,强烈建议选择CTI值高于最大工作电压的材料(例如PLC 1或0),以显著降低漏电起痕的风险。

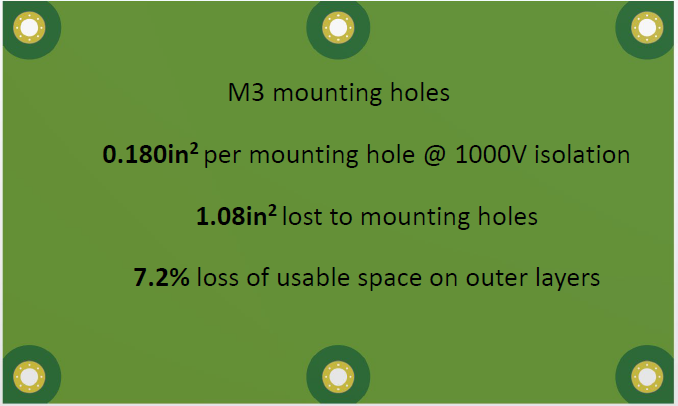

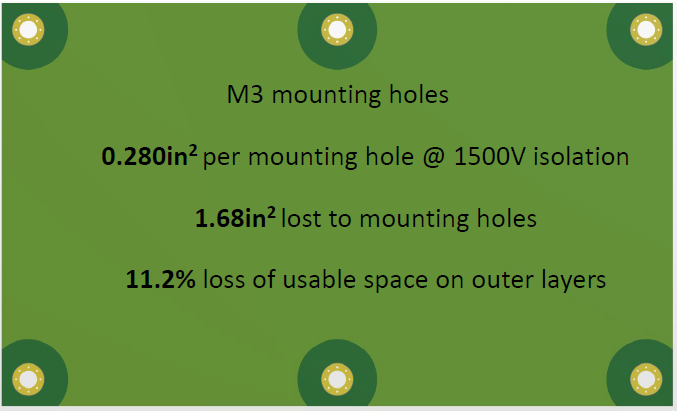

最后,更高的电压隔离需求会显著减少PCB的可用布局面积。例如,在一个3x5英寸的电路板上,安装孔所需的隔离间隙:

50V隔离:损失2.3%的可用外层空间。

1500V隔离:损失11.2%的可用外层空间。

这种面积损失会严重影响布线密度和元件布局。因此,在项目初期就明确电压需求至关重要,这可以避免在设计后期因空间不足而进行昂贵的返工。

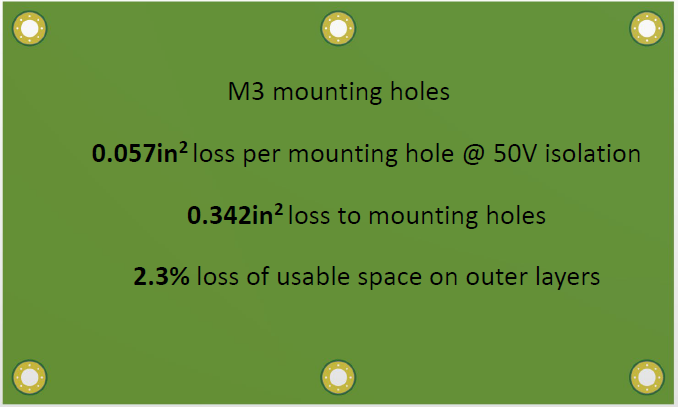

结合 Saturn PCB tools,以下是 50 V 的示例(3x5英寸 PCB):

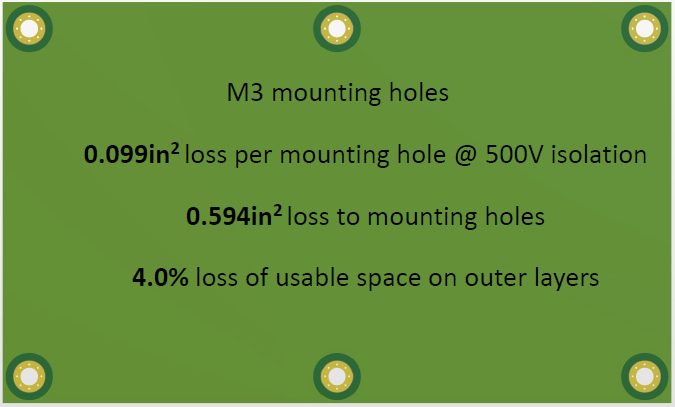

以下是 500V 的示例(3x5英寸 PCB):

以下是 1000V 的示例(3x5英寸 PCB):

以下是 1500V 的示例(3x5英寸 PCB):

可以看到,电压隔离要求对可用的布局、布线区域有不小的影响。如果可能的话,尽量在原理图中也清晰地标记电压隔离的需求。必须在 EDA 工具中设定爬电距离和信号间距的规则,不要依靠人工的检查!

我要赚赏金

我要赚赏金