光耦兼容型隔离驱动输入侧电路配置应用笔记

光耦兼容型输入隔离驱动

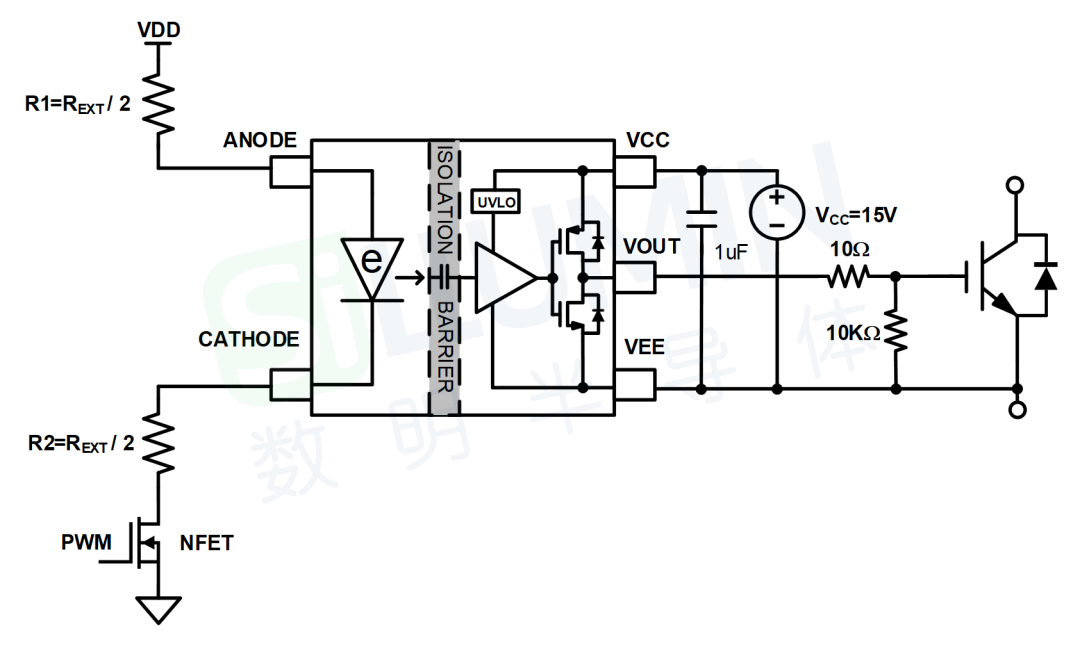

对于光耦兼容型输入的隔离驱动,比如 SiLM5343AT,它的输入级是属于电流型驱动。它不像 TTL 或 COMS 这种电压型输入需要特定的电压来驱动。如图 1 所示,它的输入级是一个模拟的电子二极管,当流经这个二极管的电流大于电流阈值(IF)时,驱动输出电压(VOUT)就为高,而当输入端没有电流时,驱动输出电压为低。

图 1. 光耦兼容型输入的隔离驱动框图

本文会介绍两种常用的光耦兼容输入侧配置电路。对讨论的参数基于SiLM5343AT:

模拟电子二极管电压:VF= 2.1V ~ 2.5V (推荐值 2.25V)

模拟电子二极管电流阈值:IF= 10mA (推荐工作范围 7mA ~ 16mA)

输入结构:缓冲器配置

输入缓冲器结构是输入信号(一般是由 MCU/DSP 提供的 PWM 信号)经过缓冲器(buffer)后接到输入阳极 Anode,由缓冲器来提供电流,如图 2 所示。

图 2. 输入缓冲器配置

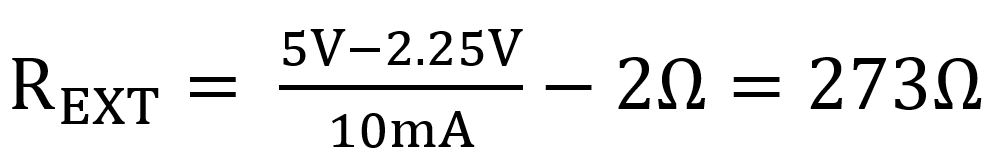

图2的外部电阻 REXT取值参考如下公式

如果 VDD=5V, 缓冲器选择 SN74LVC2G17, ROH_BUFFER=22Ω,那么

在图 2 中,REXT是分成了两个电阻 R1,R2 分别置于 ANODE 和 CATHODE 管脚处。这种上下对称的配置方式有助于改善系统输入级对共模干扰信号的抑制。实际可以取 R1=R2=130Ω。

输入结构:MOSFET开关配置

另一种输入侧配置电路是通过一个开关管,比如一个 MOSFET 来控制输入侧的电流,如图 3。在这种结构中,PWM 通过控制 NFET 的开、关来控制流经模拟电子二极管的电流,从而控制驱动输出。

图 3. MOSFET控制输入电流开关

图 3 的外部电阻 REXT取值参考如下公式。

如果 VDD=5V, NFET 选择 2N7002, 它的 RDS_ON=2Ω,那么

NFET 也可以替换为达林顿晶体管,比如 ULN2003A,这种情况下外部电阻 REXT取值公式如下。

如果 VDD=5V, VCE_SAT=0.75V, 那么

ANODE 和 CATHODE 间并联电阻

在实际应用中,基于图 2 和图 3 两种输入配置电路,在芯片引脚 ANODE 和 CATHODE 之间并联合适的电阻,可以提供输入信号关断时快速泄放路径,如图 4。

图 4. ANODE和CATHODE间并电阻

对于图 4 中并联电阻计算公式如下:

因为模拟电子二极管的 IF 推荐的最小值是 7mA, 如果 VDD=5V,REXT=273Ω, RDS_ON=2Ω,

那么

所以 RPARAL不能小于 750Ω,建议可以取 1kΩ。

ANODE 和 CATHODE 间并联电容

在一些应用中,输入控制信号线很长,容易引入高频噪声。此时可以选择在 ANODE 和 CATHOHDE 间并联电容,滤除输入信号上的高频毛刺,同时也能吸收关断状态时刻在 ANODE 和 CATHODE 之间的瞬态震荡能量。

图 5. ANODE 和 CATHODE 间并电容

并联的电容不能太大,建议取值范围 100pF ~ 470pF。如果电容过大,会导致 RC 时间常数大,从而影响传输延迟时间。下图为输入侧并联电阻 1kΩ 以及并联电容为 220pF 和 2.2nF 时的传输延迟对比波形。从这个测试结果看,在 2.2nF 的时候,传输延迟时间变得非常大了。

通道信息:CH3: VPWM CH4: VOUT

TPLH=88.4ns

(RPARAL=1kΩ, CPARAL=220pF)

TPHL=112.4ns

(RPARAL=1kΩ, CPARAL=220pF)

TPLH=213.6ns

(RPARAL=1kΩ, CPARAL=2.2nF)

TPHL=424.4ns

(RPARAL=1kΩ, CPARAL=2.2nF)

图 6. ANODE 和 CATHODE 间并联电容的测试

我要赚赏金

我要赚赏金