一、概述

扇出型晶圆级封装(FOWLP)的概念最早由德国英飞凌提出,自2016 年以来,业界一直致力于FOWLP 技术的发展。这种封装架构具有较大的灵活性,适用于多样的应用场景,能够在晶圆级别上集成多种功能芯片,包括逻辑、存储器、功率IC、射频和无源元件等,从而实现多功能、高性能和低功耗的目标。扇出型封装是指芯片焊盘通过扇出方式从芯片的边缘通过RDL 和焊球与PCB 连接,图 为扇出型晶圆级封装结构以及扇出区域演示图。RDL 工艺有效地增加了芯片可用的布线区域,并降低了成本。目前,扇出型封装基本分为3 类:先上晶芯片面朝上(Chip First-Face Up),先上晶芯片面朝下(Chip First-Face Down),后上晶(Chip Last)或称先RDL(RDL First)。与Chip First 工艺相比,Chip Last(RDL First)工艺具有更高的复杂度和制作成本。

扇出型晶圆级封装结构以及扇出区域演示图

扇出型晶圆级封装不仅已在移动设备领域广泛应用(如用于封装处理器、存储器及射频芯片),其应用范围也正逐步拓展至汽车电子(如处理器、传感器与控制单元封装)、人工智能(如学习芯片、神经网络处理器封装)以及物联网等多元化领域。其灵活的封装架构与多功能特性,使得该技术能够满足不同应用场景下的多样化需求。目前,市场上已有多款代表性产品采用了扇出型晶圆级封装技术,例如苹果A10芯片、赛灵思ACAP自适应计算平台以及英特尔Lakefield芯片等。

二、封装技术

1.台积电InFO 技术

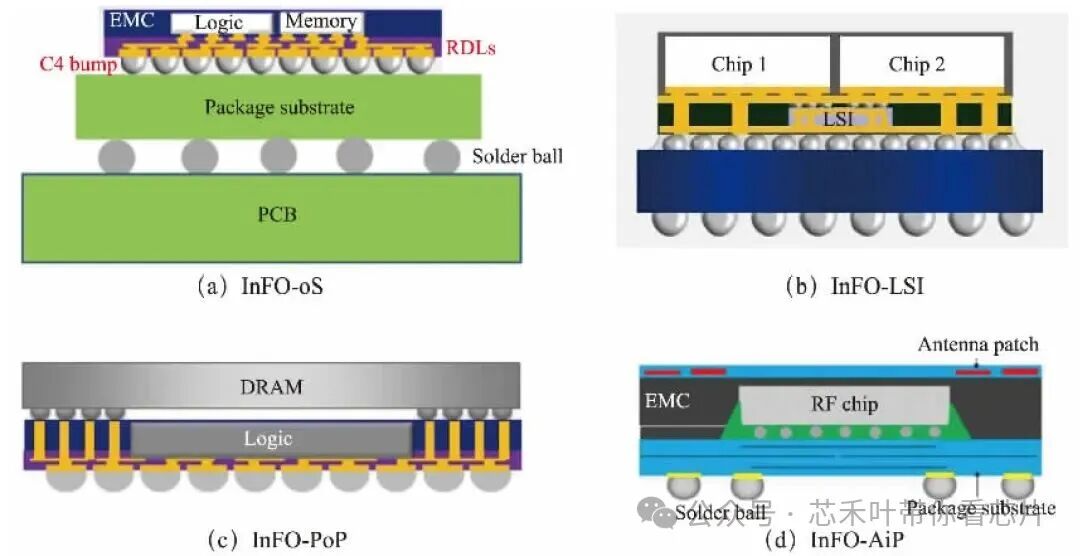

InFO 技术是台积电在2016年推出的一项扇出型封装技术。该技术的核心是将芯片直接放置于基板上,通过再分布层(RDL)实现芯片与基板之间的电气互连,无需采用传统的引线键合方式。RDL形成于晶圆表面,可对键合焊盘进行重新布局,提供更大的焊盘间距,从而支持更多的I/O连接,实现更紧凑和高效的系统设计。该技术最早应用于2016年发布的苹果A10芯片,并已发展出多个衍生技术方向,包括InFO-oS、InFO-LSI、InFO-PoP以及InFO-AiP等。图展示了InFO技术及其主要衍生应用的封装结构示意图。

InFO-oS技术能够集成多个先进逻辑芯片,在封装内部实现更高的集成密度,尤其适用于5G网络设备等场景。InFO-LSI技术在功能上与英特尔的嵌入式多芯片互连桥接技术类似,致力于在互连带宽与成本之间实现最优平衡。该技术采用硅基互连方式,实现不同芯片层之间的高密度连接,支持同一封装内部的高速信号传输,从而提升系统整体性能与能效。InFO-LSI技术主要面向高性能计算、人工智能、通信与网络设备等对高速信号传输与处理有严格要求的领域,具有重要的应用价值。

InFO-PoP技术是InFO与堆叠封装(PoP)技术的结合,适用于需集成多颗芯片的应用场景(如移动设备),有助于实现更高的集成度与功能复杂度。InFO-AiP技术则是在InFO封装中直接集成天线,可实现更紧凑的器件布局与更优的信号传输性能。该技术常见于移动终端、物联网设备及通信设备等领域,能够显著提升无线连接性能。

InFO 技术及其衍生应用的封装结构示意图

2. FOWLP 在MEMS 传感器封装中的应用

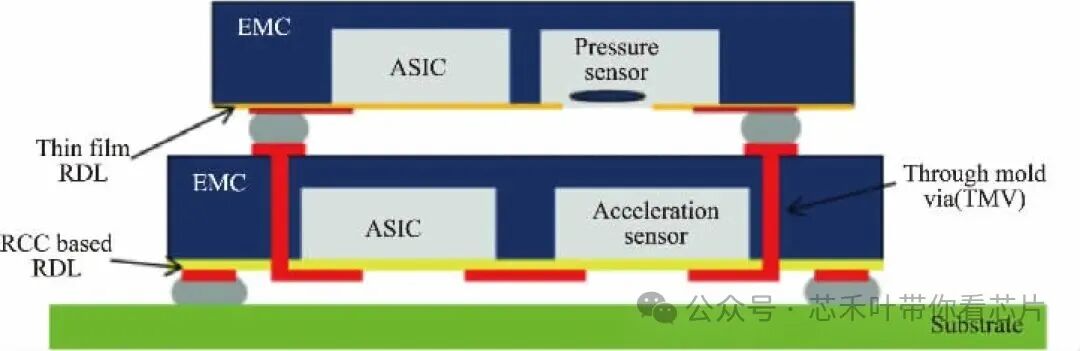

FOWLP 技术可用于实现多传感器堆叠。压力传感器和专用集成电路(ASIC)堆叠封装结构如图 所示,该封装结构被组装在一个加速度传感器和ASIC封装的背面,并通过模具通孔实现3D 布线。压力传感器的封装采用了Chip First 方法和基于薄膜的RDL的FOWLP 技术;加速度传感器和ASIC 的封装采用了基于双面树脂涂层铜重新分配的FOWLP 技术。该技术的优点是可以直接实施激光钻孔,以实现从封装底部到顶部的3D 布线。

压力传感器和ASIC 堆叠封装结构

在人工智能和5G 通信等产品的推动下,FOWLP技术在移动通信、高性能计算、自动驾驶汽车和物联网等领域展现出广泛的应用前景。Chip First 封装形式适用于便携式、移动和可穿戴产品,以及射频/模拟、PMIC、AP、低端ASIC、CPU 和GPU 等IC 的封装。预计未来5 年内,Chip First 将成为最常用且广泛应用的封装方式。而针对高端CPU、GPU、ASIC 以及超级计算机、服务器、网络和电信产品的FPGA 等IC 器件,Chip Last(RDL First)的封装形式可能更为适用。

我要赚赏金

我要赚赏金