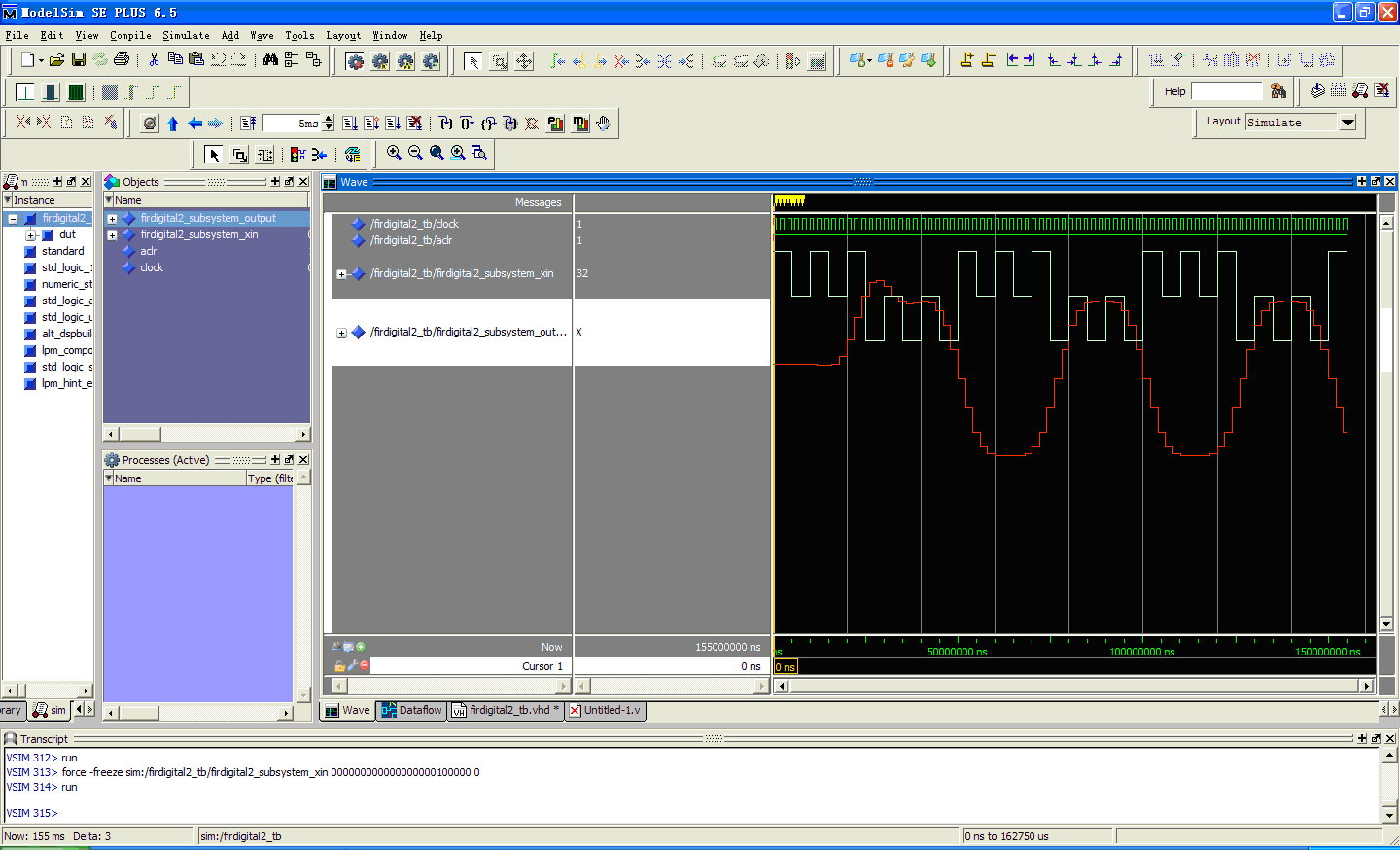

用DSP-BUILDER在SIMULINK中生成模块(只加输入和输出的24位ALTBUS,中间无任何器件模块,仅为了测试MODELSIM仿真),然后用SIGNAL COMPILER输出VHDL文件,打开MODELSIM将其编译,然后用VERILOG写了TESTBENCH,但运行前仿真时,输出无信号(为红线U)。求救!!TESTBENCH是找例子改的,小弟初来乍到,请大家多批评指教

(以下是SIGNAL COMPILER生成HDL文件和用VERILOG写的TESTBENCH)

DUT:

-- This file is not intended for synthesis, is is present so that simulators

-- see a complete view of the system.

-- You may use the entity declaration from this file as the basis for a

-- component declaration in a VHDL file instantiating this entity.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.NUMERIC_STD.all;

entity firdigital1 is

port (

Clock : in std_logic;

aclr : in std_logic;

firdigital1_Subsystem_Output : out std_logic_vector(33-1 downto 0);

firdigital1_Subsystem_Output1 : out std_logic_vector(24-1 downto 0);

firdigital1_Subsystem_Xin : in std_logic_vector(24-1 downto 0)

);

end entity firdigital1;

architecture rtl of firdigital1 is

component firdigital1_GN is

port (

Clock : in std_logic;

aclr : in std_logic;

firdigital1_Subsystem_Output : out std_logic_vector(33-1 downto 0);

firdigital1_Subsystem_Output1 : out std_logic_vector(24-1 downto 0);

firdigital1_Subsystem_Xin : in std_logic_vector(24-1 downto 0)

);

end component firdigital1_GN;

begin

firdigital1_GN_0: if true generate

inst_firdigital1_GN_0: firdigital1_GN

port map(Clock => Clock, aclr => aclr, firdigital1_Subsystem_Output => firdigital1_Subsystem_Output, firdigital1_Subsystem_Output1 => firdigital1_Subsystem_Output1, firdigital1_Subsystem_Xin => firdigital1_Subsystem_Xin);

end generate;

end architecture rtl;

TESTBENCH:

module testbench;

//module_item

reg aclr;

reg clock;

reg [23:0] firdigital1_subsystem_xin;

wire [32:0] firdigital1_subsystem_output;

wire [23:0] firdigital1_subsystem_output1;

firdigital1 dut(.clock(clock),

.aclr(aclr),

.firdigital1_subsystem_xin(firdigital1_subsystem_xin),

.firdigital1_subsystem_output(firdigital1_subsystem_output),

.firdigital1_subsystem_output1(firdigital1_subsystem_output1));

initial begin

clock = 0;

forever #2 clock = ~clock;

end

initial begin

aclr = 1;

firdigital1_subsystem_xin = 5'b00000;

#2

aclr = 0;

firdigital1_subsystem_xin = 5'b00001;

#2

aclr = 1;

firdigital1_subsystem_xin = 5'b00000;

#2

aclr = 0;

#2

firdigital1_subsystem_xin = 5'b00001;

#2

#1000 $stop;

end

initial begin

$timeformat(-3,1,"ms",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

end

endmodule;

我要赚赏金

我要赚赏金