10.20

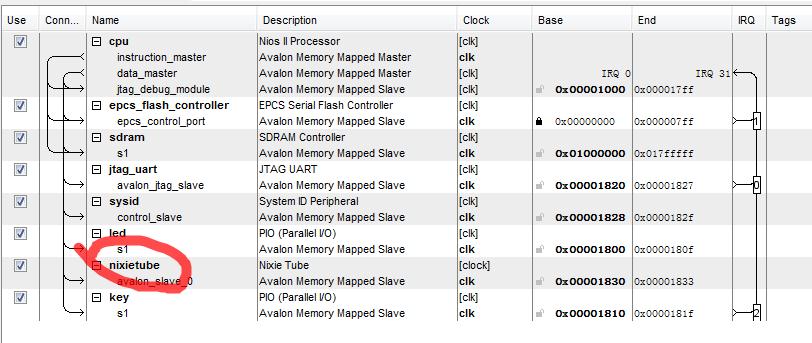

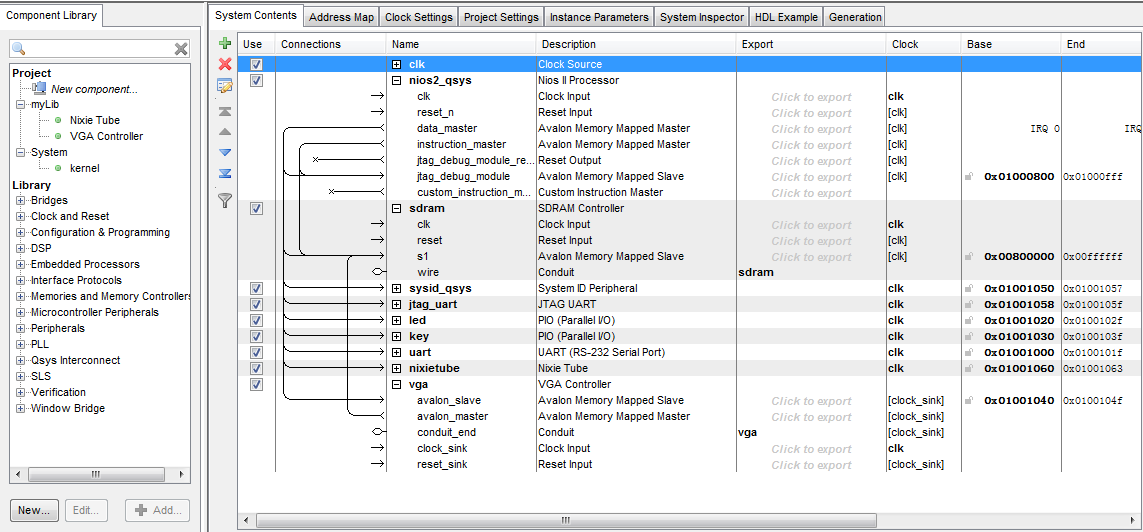

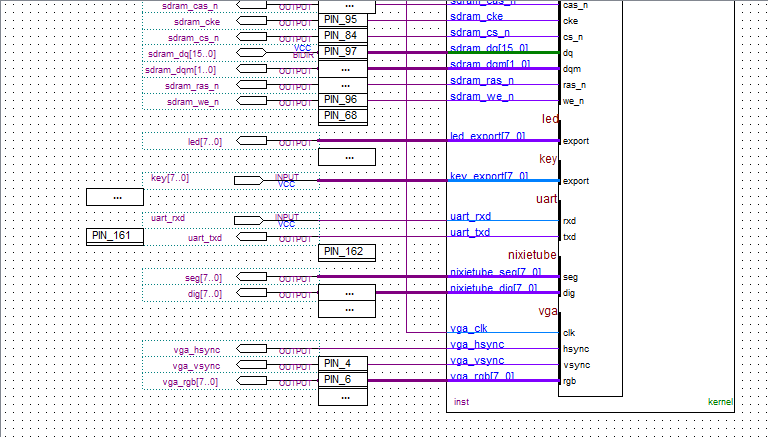

继续学习Nios II。需要设计自己的IP,研究了些资料,先制作数码管的IP核。

修改之前seg.v的代码。思路是通过avalon总线发送32bits数据,每4bits代表一个数码管,可以显示0~F。8个数码管动态刷新。

代码:

// SEG数码管模块

module seg_ip(

input clk, // 系统时钟输入,50MHz

input reset_n, // 系统复位输入

input write,

input [31:0]writedata,

output[7:0] seg, // seg输出

output[7:0] dig // dig输出

);

reg[6:0] seg_r;

reg[7:0] dig_r;

assign seg = { 1'b1, seg_r };

assign dig = dig_r;

reg[15:0] scan; //扫描

reg[31:0] seg_data;

//扫描时钟

always @(posedge clk or negedge reset_n)

begin

if(!reset_n)

scan = 16'd0;

else

scan = scan + 1'b1;

end

always @(posedge clk or negedge reset_n)

begin

if(!reset_n)

seg_data[31:0] <= 31'd0;

else if(write)

seg_data[31:0] <= writedata[31:0];

end

//片选

always @(scan[15:13])

begin

case(scan[15:13])

3'd0: begin dig_r <= ~8'h01; seg_r <= trans(seg_data[3:0]); end

3'd1: begin dig_r <= ~8'h02; seg_r <= trans(seg_data[7:4]); end

3'd2: begin dig_r <= ~8'h04; seg_r <= trans(seg_data[11:8]); end

3'd3: begin dig_r <= ~8'h08; seg_r <= trans(seg_data[15:12]); end

3'd4: begin dig_r <= ~8'h10; seg_r <= trans(seg_data[19:16]); end

3'd5: begin dig_r <= ~8'h20; seg_r <= trans(seg_data[23:20]); end

3'd6: begin dig_r <= ~8'h40; seg_r <= trans(seg_data[27:24]); end

3'd7: begin dig_r <= ~8'h80; seg_r <= trans(seg_data[31:28]); end

endcase

end

//译码任务

function [6:0] trans;

input [3:0] in_data;

begin

case(in_data[3:0])

0: trans = 7'b100_0000; // 0

1: trans = 7'b111_1001; // 1

2: trans = 7'b010_0100; // 2

3: trans = 7'b011_0000; // 3

4: trans = 7'b001_1001; // 4

5: trans = 7'b001_0010; // 5

6: trans = 7'b000_0010; // 6

7: trans = 7'b101_1000; // 7

8: trans = 7'b000_0000; // 8

9: trans = 7'b001_1000; // 9

10: trans = 7'b000_1000; // A

11: trans = 7'b000_0011; // b

12: trans = 7'b100_0110; // c

13: trans = 7'b010_0001; // d

14: trans = 7'b000_0110; // E

15: trans = 7'b000_1110; // F

default: trans = 7'b111_1111;

endcase

end

endfunction

endmodule

在IDE端,测试程序修改为:

#define seg *(volatile unsigned int *) NIXIETUBE_BASE

seg = data++;

按键一次,数据+1

我要赚赏金

我要赚赏金