此贴将会是 q王在在 在本次CPLD_DIY活动中的开发进程贴。

这个月中旬收到的板子的器件包。但是那一段时间比较忙,而且是第一次焊贴片的(引脚还这么密),所以就一直没有动手。但是看到好多人都焊好了,我就有点紧张,抽时间先焊了,测试程序可用,就先开个进程贴,然后慢慢学。

下面是自己焊接及调试的一些图片,希望大家多多交流。

程序的下载:

其实就和单片机下载HEX文件差不多。只不过下载软件变成QUARTUS II 自带的,下载文件的格式变成.QOF格式。

下面看具体操作。

注:论坛上传视频太麻烦了,而且也看到论坛的出相关的教程了,所以就算了吧。

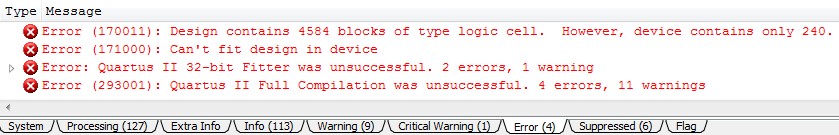

芯片的逻辑单元是有限的,比如我们用的就只有240个。超过了就会报错。这就要我们在编程时注意代码的效率。比如:

1、if...else等含有else的语句,在使用if语句的门闩功能时就会省掉else,这就使得该语句属于不完整的条件表达式,会生成一个含有7位寄存器的结构,引起电路不必要的开销。

2、在定义变量和信号类型的时候,最好规定范围,比如用到整形的时候,我只用到0~9这十个数字,那定义语句为: signal gewei : integer range 0 to 9 ; 它比不规定范围的语句: signal gewei : integer; 要节省好多资源。

3、尽量少用乘法和除法,因为这两个运算占用的资源太多。可以用其他的逻辑语句和加减来代替的尽量代替。

总之VHDL语言是一门严格精确的语言,在使用时注意代码的效率。

在VHDL语言教程中讲了好多语句,有些语句只能在仿真时可以使用,不能进行逻辑综合。比如wait语句、断言语句等,很明显这些只能在软件仿真调试时使用,根本不能综合下载到芯片中,所以在综合编译的时候就会出错。这个得注意。

还有就是VHDL中的延时问题,一开始以为可以使用wait语句来延时,没有想到一直出错,才知道不能进行逻辑综合的意思。在VHDL中要进行延时可以利用时钟通过分频来实现,比如我们使用的是50M晶振,通过计数50M就可以定时1S,依次类推,而且定时非常准确,定时精度就看使用晶振的频率了,晶振频率越高,定时精度就越高。

有不对的地方欢迎大家指正,正在学习过程中。。。