分享一下学习资料

特性

暂略

简介暂略

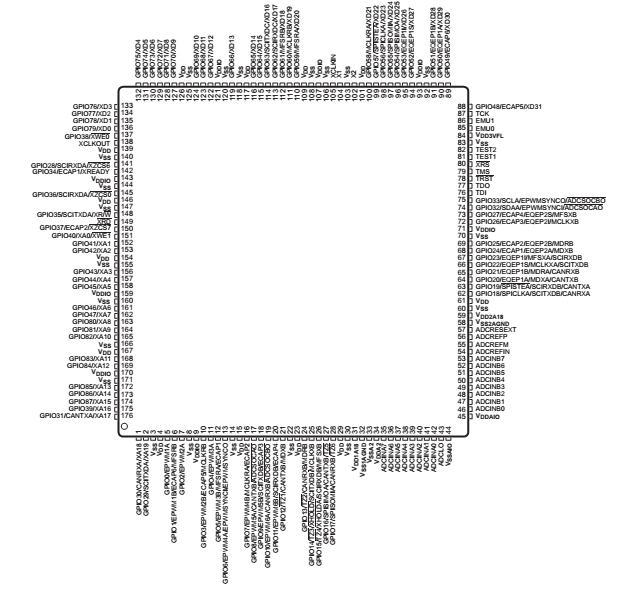

引脚有LQFP、BGA、PBGA封装,开发板用的是LQFP

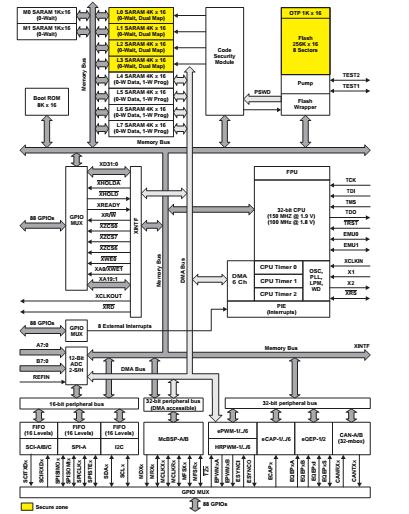

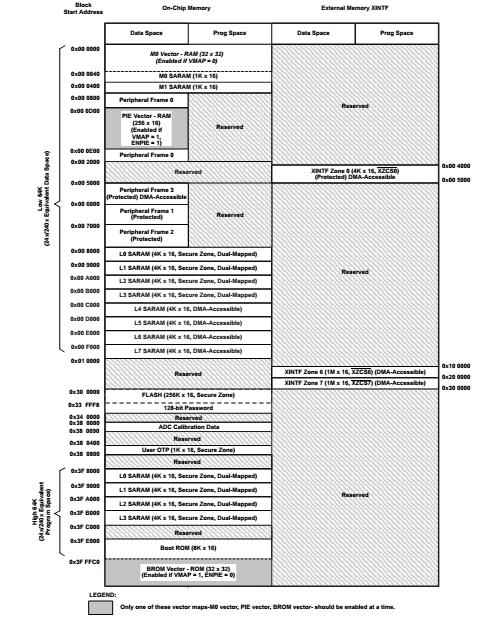

待有时间详细分析

待有时间详细分析

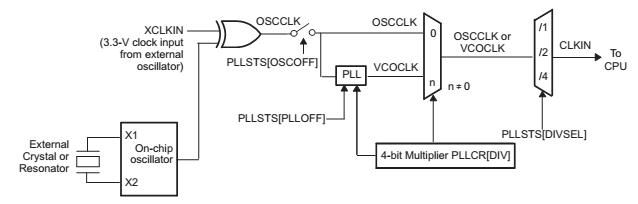

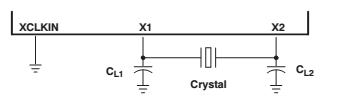

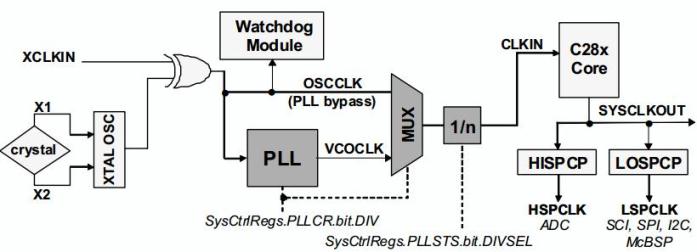

该器件可由一个外部振荡器计时或者由一个连接到片载振荡器电路的晶振计时。提供的一个PLL支持高达1031个输入时钟缩放比。PLL比率可用软件中在器件运行时更改,这使得用户在需要低功耗运行时能够按比例降低运行频率。时序细节,请参考电气规范部分。PLL块可被设定为旁路模式。

OSC和PLL块

使用内部振荡器,30MHz外部石英晶振

使用内部振荡器,30MHz外部石英晶振

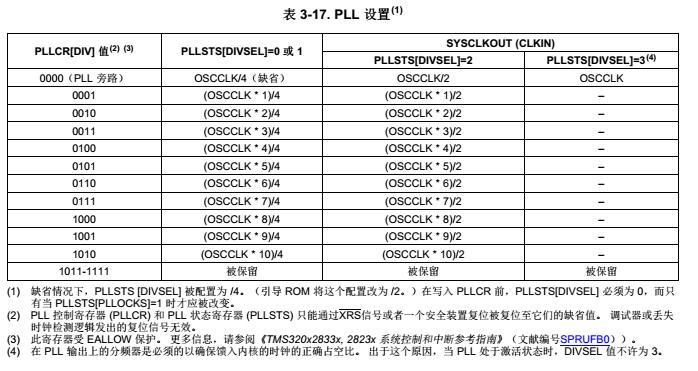

基于PLL的时钟模块

此器件有一个片载、基于PLL的时钟模块。这个模块为器件提供所有需要的时钟信号,以及对低功耗模式进入的控制。PLL有一个4位比率控制PLLCR[DIV]来选择不同的CPU时钟速率。在写入PLLCR寄存器之前,安全装置模块应该被禁用。在PLL模式稳定后,它可被重新启用(如果需要的话),重新启用的时间为131072个OSCCLK周期。输入时钟和PLLCR[DIV]位应该在PLL (VCOCLK)的输出频率不超过300MHz时候选择。

基于PLL的时钟模块

此器件有一个片载、基于PLL的时钟模块。这个模块为器件提供所有需要的时钟信号,以及对低功耗模式进入的控制。PLL有一个4位比率控制PLLCR[DIV]来选择不同的CPU时钟速率。在写入PLLCR寄存器之前,安全装置模块应该被禁用。在PLL模式稳定后,它可被重新启用(如果需要的话),重新启用的时间为131072个OSCCLK周期。输入时钟和PLLCR[DIV]位应该在PLL (VCOCLK)的输出频率不超过300MHz时候选择。

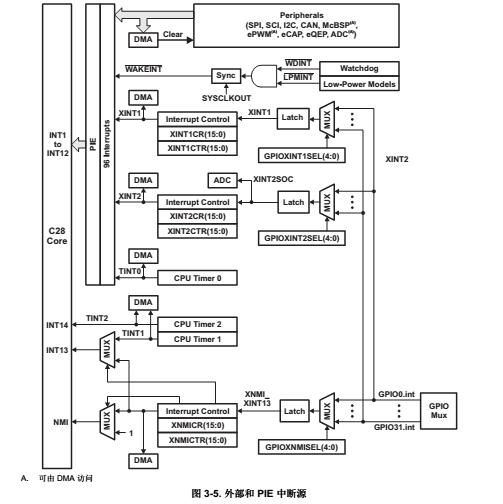

中断

用户中断分为三部分:外设级、PIE级、CPU级

三级串联构成一路中断。

外设中断扩展 (PIE)块

PIE块将许多中断源复用至中断输入的较小的集合中。PIE块能够支持多达96个外设中断。在2833x/2823x中,96中断中的58个被外设使用。96个中断被分成8组,每组被提供 12个CPU中断线(INT1或者INT12)中的1个。96个中断中的每一个中断由其存储在一个可被用户写覆盖的专用RAM块中的矢量支持。在处理这个中断时,这个矢量由CPU自动抽取。抽取这个矢量以及保存关键CPU寄存器将花费 8个CPU时钟周期。 因此CPU能够对中断事件作出快速响应。 可以通过硬件和软件控制中断的优先级。每个中断都可以在PIE块内启用或禁用。

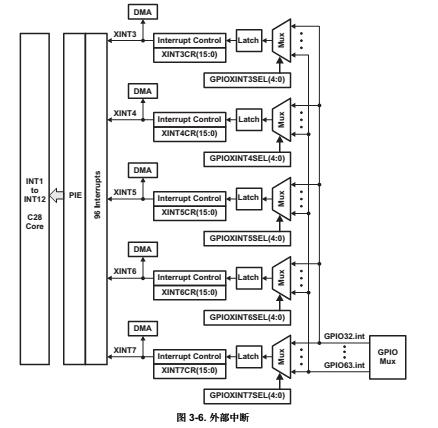

外部中断 (XINT1-XINT7,XNMI)

此器件支持 8个被屏蔽的外部中断 (XINT1–XINT7, XNMI)。 XNMI 可被连接至 INT13 或者 CPU 的 NMI 中断。 这些中断中的每一个可被选择用于负边沿、正边沿或者正负边沿触发,并且可被启用或禁用(包括XNMI 在内)。 XINT1, XINT2,和 XNMI 还包含一个 16位自由运行的上数计数器,当检测到一个有效的中断边沿时,该计数器复位为 0。 这个计数器可被用于为中断精确计时。 与 281x 器件不同,没有用于外部中断的专用引脚。 XINT1,XINT2 和 XINT 中断可接受来自 GPIO0-GPIO31 引脚的输入。 XINT3–XINT7 中断可接受来自 GPIO32-GPIO63 引脚的输入。

整个时钟电路的原理框图如图所示。

在使用有源晶振作为外部的时钟源时,DSP片内的晶体振荡电路会被旁路,外部的时钟信号有XCLKIN管脚输入DSP。看门狗定时器取OSCCLK信号作为其输入。C28x的内核会将输入的CLKIN信号转换为SYSCLKOUT信号(这就是通常我们提到的那些150MHz的信号)。SYSCLKOUT主要用来为DSP片上的一些外设提供时钟信号。按照外设的速率,一般分为需要高速时钟信号HSPCLK(顾名思义即high speed peripheral clock)的外设,如EPWM、ADC等等;以及仅需要较低的信号频率LSPCLK(顾名思义即low speed peripheral clock)的外设,主要是一些串行设备,如SCI、SPI、I2C、McBSP等。HSPCLK与LSPCLK都是通过对SYSCLKOUT进行分配得到的,主要是通过配置寄存器的控制位实现不同的分频因子。举例如下:

|

HSPCLK/ LSPCLK |

外设时钟频率 |

|

0 0 0 |

SYSCLKOUT |

|

0 0 1 |

SYSCLKOUT / 2 |

|

0 1 0 |

SYSCLKOUT / 4 |

|

0 1 1 |

SYSCLKOUT / 6 |

|

1 0 0 |

SYSCLKOUT / 8 |

|

1 0 1 |

SYSCLKOUT / 10 |

|

1 1 0 |

SYSCLKOUT / 12 |

|

1 1 1 |

SYSCLKOUT / 14 |

HSPCLK的上电默认值是SYSCLKOUT / 2,即在SYSCLKOUT为150MHz的情况下,HSPCLK默认为75MHz,所以如果想让外设工作在最高频率下一定不能忘了设置这些位。此外,如果没有正确配置的话,那外设里面的定时器,如PWM定时器的周期都将与预想的产生倍数倍的错位。LSPCLK的默认值则为SYSCLKOUT / 4。

在SysCtrlRegs.PCLKCR0、SysCtrlRegs.PCLKCR1、SysCtrlRegs.PCLKCR3寄存器中,有对各个外设时钟信号的单独的使能控制。比如,我们禁止掉SysCtrlRegs.PCLKCR0里面的ECANBENCLK,则ECANB模块没有时钟信号输入,其消耗的功率就近乎为0了。(为什么?因为CMOS电路的功耗主要是动态功耗啊!)

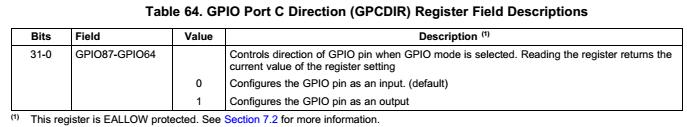

看原理图,用的是GPIO64~71

作为最常用的输入引脚,主要配置功能选择和方向选择

所以程序的关键配置代码:

//设置DSP部分的按键和拨码开关相关管脚

EALLOW;

//管脚功能选择

GpioCtrlRegs.GPCMUX1.bit.GPIO64 = 0; // KEY3

GpioCtrlRegs.GPCMUX1.bit.GPIO65 = 0; // KEY2

GpioCtrlRegs.GPCMUX1.bit.GPIO66 = 0; // KEY1

GpioCtrlRegs.GPCMUX1.bit.GPIO67 = 0; // KEY0

GpioCtrlRegs.GPCMUX1.bit.GPIO68 = 0; // SW1-P1

GpioCtrlRegs.GPCMUX1.bit.GPIO69 = 0; // SW1-P2

GpioCtrlRegs.GPCMUX1.bit.GPIO70 = 0; // SW1-P3

GpioCtrlRegs.GPCMUX1.bit.GPIO71 = 0; // SW1-P4

//输入输出方向设定

GpioCtrlRegs.GPCDIR.bit.GPIO64 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO65 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO66 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO67 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO68 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO69 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO70 = 0;//input

GpioCtrlRegs.GPCDIR.bit.GPIO71 = 0;//input

EDIS;

使用的是查询方式,无限循环查询输入:

while(1)

{

//读取按键对应的管脚状态

KeyValue = GpioDataRegs.GPCDAT.all & 0x000000FF;

}

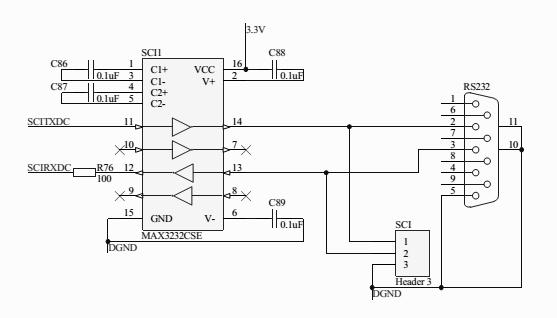

Quartus II 10软件没下完,也不敢先动CPLD,LED的实验先放下了,看看串口吧

串行通信接口 (SCI) 模块 (SCI-A,SCI-B,SCI-C)

该器件包括三个串行通信接口(SCI)模块。 SCI 模块支持 CPU 与其它异步外设之间的使用标准非归零码

(NRZ) 格式的数字通信。 SCI 接收器和发射器是双缓冲的,并且它们中的每一个有其自身独立的使能和中断

位。 两个器件都可独立或者同时地运行在全双工模式。 为了确保数据完整性,SCI 在中断检测、奇偶校

验、超载、和组帧错误方面对接收到的数据进行检查。 通过一个 16 位波特率选择寄存器,可将比特率设定

为超过 65000 个不同的速度。开发板引出的是SCI-C口

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |