自1970年发明MOS工艺及73年推出CMOS工艺以来,至今还没有发现可替代它的工艺,足见CMOS工艺的经济合理性。因此,至今硅基材料的应用仍在继续延伸。然而,在晶体管工艺制造中采用二氧化硅作为栅极材料,实质上已逼近极限。如65纳米工艺时,二氧化硅栅极的厚度己降低至1.2纳米,约5个硅原子层厚度,如果再继续缩小,将导致漏电及功耗急剧上升。

晶体管工艺技术的又一个里程碑

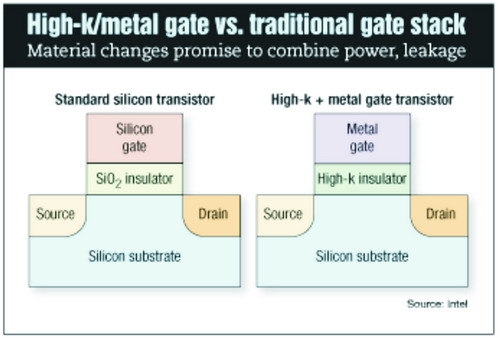

Intel共同创始人Gordon Moore说,采用“high-k”和金属栅电极材料,标志着从推出多晶硅栅MOS晶体管以来,晶体管技术的一个最大的突破,具有里程碑作用。高k及金属栅结构与传统的晶体管栅结构比较如图1所示。

图1 高k及金属栅结构与传统的晶体管栅结构比较

在半导体制造工艺中采用二氧化硅作为栅介质材料及多晶硅作为栅电极材料的组合已经成功地运行了30多年,一直使用到90纳米节点还相安无事。之后在65纳米工艺节点时才发现漏电流及功耗急速上升,开始引起业界的警觉。虽然也曾采用如引变硅等技术来继续延伸,但是自进入45纳米节点后,矛盾日趋突出,如果想继续缩小尺寸,就必须采用新的

材料。

45纳米是个坎

回顾历程,当2002年工业开始导入0.13微米时,曾遇到阻碍。因为芯片制造厂同时开始引入铜互连及低k介质材料对于这两种全新的工艺技术,工业显得力不从心,后来经过努力才闯过关。

如今,同样在45nm工艺时,也将面临采用193浸液式光刻及超低k介质材料,包括高k介质材料(k值在15至20)及金属栅等新工艺技术。多项新技术及新设备的同时加入,使得工业也面临同样的困境。业界一致认为,45纳米也会是工业的一个坎。反映在如TI、NXP等在内的大公司,因承受不住高昂的研发费用,而退出45纳米以下的发展, 转而与台积电合作。

Intel在2006年就披露45纳米工艺的进展情况,并声称是全球第一批采用45纳米工艺,预期到2007年下半年时量产。目前Intel己经有三个芯片厂能进行45纳米器件生产。包括俄勒冈州的DID厂、亚利桑那州的F32和以色列的Fab18。Intel预计从今年Q2(二季度)起90纳米工艺将逐渐退出,而65纳米将占产能的90%,并计划于2011年推进22纳米。

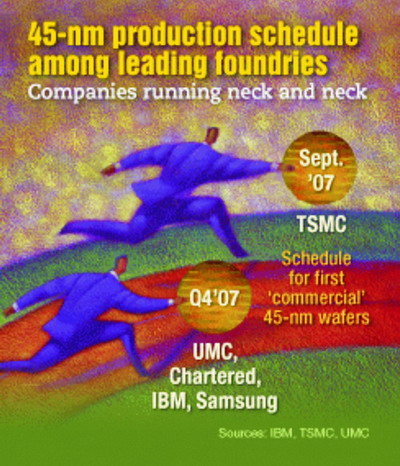

图2 主要Foundry厂商的45纳米工艺时间表

据Intel报道,改用高k介质材料后,其漏电量降为原来十分之一。另外,由于高k栅极材料与现有的硅栅电极并不相容。因此必需采用新的金属栅电极材料来增加驱动电流。而45纳米工艺可使晶体管的密度提升2倍,运作时的耗电量减30%,而总的工艺成本费用仅上升4%。

台积电最近披露其45纳米工艺,并计划在2007年第三季开始生产。台积电透露其10层金属技术,能使栅极长度减少到26纳米。

日本瑞萨与松下宣布两公司合作开发的45纳米工艺己进人全面整合测试阶段。松下与三菱早在1998年就开始高端工艺的研发,但在三菱和日立半导体合并成立瑞萨之后,瑞萨就取代三菱,并与松下联合研发130纳米,90纳米及65纳米技术。双方在开发45纳米工艺上的合作于2005年10月开始,并定于07年秋季完成,于2008年4月开始45纳米量产。日本东芝、Sony及NEC等也在积极推进45纳米工艺。

在45纳米工芝技术研发中,颇受业界关注的是特许、IBM、英飞凌和三星的联盟。它们将以低功耗工艺技术为基础,联手开发第一款45纳米的下一代通讯系统芯片。这款芯片的分工由IBM位于纽约的EastFishkill300厂生产;其标准库单元模组和I/O单元均由英飞凌提供。由于采用的是平台设计,该45纳米工艺在四家公司都可相容。并预期在07年底,可以在特许、IBM和三星的晶圆厂中同时通过认证。

采用通用平台的晶圆代工模式己经有数年,并得到电子设计自动化,EDA,知识产权(IP)与设计服务领域的合作伙伴共同支持。其目的能使客户将其芯片设计外包给不同的12英寸芯片制造厂,以尽可能地降低重复设计工作量。该联盟主席IBM的半导体研发部门副总裁LisaSu指出,45纳米技术的发布,表明该工艺技术在使用上的弹性化,而应归功于GDSII在多家制造厂所具有的广泛相容性。据初期硬体测试结果显示,采用45纳米节点的器件,从功能上比65纳米节点至少高出30%。

英飞凌计划在2009年初与联盟其它成员同步推出基于该新技术的产品,主要是针对移动通讯应用。iSuppli的LenJenlinek认为,英飞凌的主要芯片生产业务将最可能在特许半导体进行。而IBM和三星将扮演备份产能的角色。这样有助于在高需求时降低风险。可以肯定,新加坡特许因此获益最大。因为目前己有三家大厂可能委托其进行代工生产。EastFishkill联盟使其合作伙伴各自投入的研发费用,比单独开发所需的费用少很多。由于三星的SI厂、特许的Fab7和IBM的Building323厂等多个晶圆厂都使用相同的掩膜,使大家在开发认证和大量制造的成本与产品上市时间均显著地减少。

实际上,在芯片制造业中存有不同的看法。以Intel、IBM、AMD等为代表,主张在45纳米阶段就引入高k及金属栅技术;而大部分芯片制造商,包括一流代工厂,台积电等主张应推迟至32纳米节点。

从半导体工业的前景,高k及金属栅材料可使芯片工艺制造技术开始新的一轮缩小。除Intel之外,台积电、IBM、三星及UMC等都预计在07年底前将突破45纳米工艺。

实际上高k材料面临最大的挑战,在于栅极材料的基本要求,即既能形成P型晶体管,又能形成N型晶体管。工业界早

就认为应该加速过渡,但是实际应用中,在高k材料和栅电极之间要集成在一起十分困难。另外,还有边界效应(Side Effect),即阀值电压的困扰。因为在栅介质与栅电极的界面缺陷会引起相对高的阀值电压,使得驱动电流减少及功能减弱。

由于成本及其它原因,不是所有一流芯片制造商都愿意迅速向高k及金属栅过渡,如台积电在向45纳米推进中,采用三栅二氧化硅方法,并推迟高k介质材料至32纳米。在向45纳米进军中,如果有可能不采用高k及金属栅,而采用SOI,或者引变硅技术等,其效果没有那么明显,同样存有许多集成技术的困难。采用厚的铪基材料作为栅堆的高k介质材料,据Intel说,与二氧化硅相比能减少漏电流至1/10,源漏间漏电流为1/5,总的驱动电流增加20%。

Intel采用原子层淀积ALD工艺来生长高k介质材料。NEC及TI则采用另一种工艺,MOCVD及IBM正在同时评估ALD及MOCVD技术。与通常的CVD工艺相比,ALD工艺可以一次淀积一个原子,所以能控制单层薄膜的厚度及均匀性在100埃(1埃=10-10米)之内。

摩尔定律还能撑多久?

依Intel的工艺路线图, 连Intel自己也只敢写到2011年,即22纳米。反映整个工业界还较理性,目前连32纳米的光刻量产方案还有点举棋不定。因此22纳米之后究竟走向哪里,现在没有定论。可以预计,在32纳米及以下时,半导体制造己转向“材料时代”。无论如何,物理极限无法避免,所以摩尔定律总有终结的一天。目前业界笼统地表示,摩尔定律还有10年至15年,实际上如依Intel的路线图,仍坚持每两年一个台阶,到2015年时己达9纳米。所以,客观地讲,从现在算起,还有十年己足矣。

实际上,讨论还有多长时间并没有多少实际意义,16纳米或是9纳米?一则技术还在进步,想信一定会有新的替代技术呈现;另外,也可能技术本身可行,但从经济上己无法承受,俗称后摩尔的经济定律开始起作用。任何时候,可能及需要是个平衡点,市场会作最终的决定。

我要赚赏金

我要赚赏金