作为网络安全问题一种较好的解决方案,加密卡通常需要具备下列功能:

·使用密码算法对数据进行加密解密,密码算法应可更换、升级、克服硬件改动困难的缺点,保护用户投资;

·存放密钥、证书及其他必需的数据,主密钥和重要的密钥应受到保护,而且这种保护应该比通常的软件能达到的强度更高;

·与主机、外围设备和系统软件有良好接口,方便用户开发相应的高层软件。

上述要求决定了PC加密卡的设计目标以及基本结构。

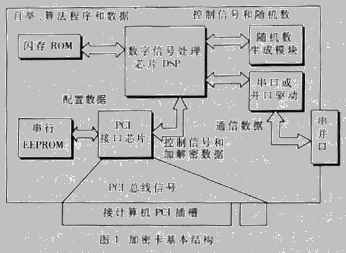

1 PC加密卡的基本结构

PC加密卡主要由主CPU、计算机总线接口、板上RAM/ROM、随机数生成模块和外部设备接口等组成。TI公司新推出的TMS320C6x系列DSP功能强,速度也非常快,但目前价格仍然太高,不适合一般加解密使用。而TMS320C54x系列具有性能适中,价格低廉,产品成熟等特点,是较好的选择。本文所介绍的PC加密卡以TMS320C54x DSP为其主CPU。TMS320C54x系列DSP的部分产品具有HPI接口,设计为容易与ISA总线相连。但基于ISA总线的产品已经处于逐渐落伍的状态,PCI总线是当前和今后一段时间PC适配卡的主要开发平台,因此需要在PCI总线平台上开发加密卡产品。

使用通用的PCI接口芯片能够减少开发时间和成本,并获得较好的数据传输性能。在众多通用的PCI接口芯片中,AMCC公司的S5920、PLX公司的PCI9050/52等芯片是从ISA到PCI总线平台平滑过渡的最佳选择,这些芯片实现了PCI目标设备的功能,提供了与ISA总线信号兼容或时序相似的本地总线信号。但从DSP和适配卡的发展方向来说,3.3V低电压的信号环境是更主流的选择,因此加密卡采用的是PLX公司的PCI9054与TI公司的TMS320LC(VC)54x的,外围信号都是3.3V电平。图1是整个加密卡的基本结构框图。

2 PC加密卡的设计

虽然PC机的CPU的速度越来越快,但是在加解密等大量科学计算面前,还是有些力不从心。而且由于加解密要占用CPU大量的时间,在加解密运算时,使计算机系统性能降低,其他工作的处理大大放慢。加密卡由于专为加解密目的设计,采用适用于科学计算的DSP芯片,因此能够减轻CPU的计算负担,提高加解密速度和整个PC的性能。目前C54x系列的DSP芯片主频已高达100MHz以上,运算能力亦能达到200MIPS的水平,并且随着工艺水平的进步,将进一步提高,C54x系列DSP采用同一套指令系统,具有极好的向下兼容特性,推出系列硬件产品可以减少软件开发的成本。

由于除C541、C542等少数芯片之外,其他C54x系列芯片的标称电压均为3.3V以下。而目前多数PCI接口芯片为5V标称电压(其中PCI9054可工作于双电压,可用于设计通用卡),因此两种芯片之间还需要信号电平的转换芯片,常用的芯片有74LVC4245等双电压驱动芯片、SN74CBTD3384等总线开关。可编程逻辑芯片、Flash ROM及A/D芯片等则均有5V和3.3V的产品,选择范围较广。采用PCI接口芯片而不是使用FPGA、CPLD等芯片来实现部分的PCI接口逻辑,主要是因为PCI接口芯片功能全而强大(例如FIFO速度快、容量大,可支持DMA方式等),而且可以减少设计失误,缩短开发周期,降低总体开发成本。

考虑到DSP中的片上RAM已经能够满足大部分程序的容量要求,而因为算法可升级,对外部存储器的写入频度较小但不可缺,所以将卡上的RAM和ROM合二为一,采用适合此项功能的闪存(Flash) ROM。选择该类型芯片可以简化设计,具体使用的是AMD公司512KB容量的29F040(5V)或29LV040(3.3V),选取该容量主要依据卡上的算法代码的大小以及所需存放密钥、证书的数量而定,这样Flash ROM除存储程序之外,还可存放数千个1024比特的公钥和同等数量的私钥,可以满足大多数安全通信系统的需要。

3 模块的功能描述

本PC加密卡所实现的主要功能有:

·数据加密解密功能:这是PC加密卡所具有的最基本的功能。PC加密卡目前封装了DES、IDEA、TUC等对称加密算法,以及RSA等公钥算法。DES作为传统的加密算法具有应用广、速度快的优点。IDEA是已公开的可用算法中速度快且安全性强的分组密码算法,具有良好的应用前景。而公钥加密算法RSA则具有较高的安全性和密钥管理方便的特点,通常用来对会话密钥加以保护。

·数字签名与认证功能:数字签名在当前的商业和金融业中已经有了广泛的应用,为满足多方面的要求,在卡中实现了签名和认证功能,主要利用RSA算法模块来实现。

·密钥管理功能:为维护PC加密卡的正常运行,密钥的产生、保存、分配与管理功能是必不可少的。由于私钥等重要密钥在卡中保存,这一功能由加密卡的配套软件与加密卡本身协同实现。卡上内置的软件设计为可自动生成RSA的一对密钥,外界软件和系统只能得到其中的公钥,而无法得到私钥的任何信息,保证密钥的安全。

上述功能的实现依赖于加密卡各模块间的协调工作,下面是各主要模块的具体功能描述:

DSP与Flash ROM构成密码算法运算和重要数据存储的平台。系统启动时,DSP从Flash ROM调入自举和主控程序,接收主机送来的指令和数据,调入相应的算法程序,对数据进行加密或解密处理后,由主机通过PCI接口芯片读出(见图2)。

在这里可编程逻辑芯片主要实现Flash ROM的读写信号和C54x外部等待状态的生成。因为目前多数Flash ROM的读写速度跟不上DSP芯片的速度,除了DSP芯片的内部等待状态(最多7个DSP时钟周期)之外,还要加上外部等待状态。下面就是一个生成8时钟周期等待状态的模块(不使用MSC#信号),修改Q寄存器的数目和计数器的计数值,可以任意添加或减少等待状态至最佳状态。

START node istype 'reg_d';

Q0,Q1,Q2,Q3 node istype 'reg_d';

COUNT=[Q3,Q2,Q1,Q0];

START.D=1;

START.CLK=!OE#!WE;

START.AR=Q3;

COUNT:=(COUNT+1)&START#COUNT&!START;

COUNT.AR=!START*Q3;

COUNT.CLK=CLK;

READY=!START;

PCI接口芯片、串行EEPROM与可编程逻辑芯片构成与主机的接口模块,使主机与DSP之间可以透明的交换指令和数据。另外,PCI接口模块提供了PCI配置功能,支持Windows平台的即插即用,最大程度的方便用户的安装与使用。

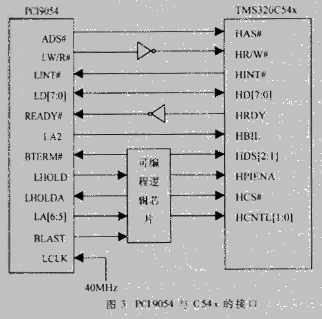

PCI9054同步的Local总线与C54x异步的HPI接口之间需要信号逻辑转换,该功能由可编程逻辑芯片方便地实现。图3是PCI9054与3.3V的LC54x芯片HPI口的连接示意框图,其中的PCI9054工作在32位Local总线,非突发的目标设备读写模式。

LHOLDA由LHOLD延迟一个Local总线时钟周期得到,并在反相后接到DSP的HCS脚。其他主要信号的基本时序关系见图4。

根据芯片的时序数据,在保证PCI9054的工作时序与LC54x的HPI口的时序满足要求的条件下,Local总线可以工作在40MHz以上。

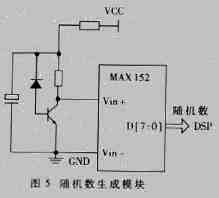

随机数生成模块的功能是产生真正意义上的随机数,而不是由软件通常所产生的伪随机数。真随机数在密码技术中的用途有:产生工作密钥和会话密钥,为公钥算法提供生成素数所需的随机数,某些公钥算法和协议(例如密钥交换协议等)直接需要一个或多个随机数参与运算等。模块生成随机数的机理源于大自然中永恒的噪声,将元器件(例如雪崩二极管)所固有的噪声加以放大,再通过A/D芯片采样转换,便得到了真正意义上的随机数。本文设计的PC加密卡该模块使用的器件较少,而且采用的A/D芯片MAX152的转换精度仅为8位,因此成本很低,而所产生的随机数足以满足一般对随机数性能的要求。仅采用D0即LSB作为所生成的随机数,其产生速率亦可达100Kbit/s以上。图5是一个简易而实用的随机数生成电路的示意图。

总之,本文描述了一种低成本、高性能的数据加解密硬件解决方案——PC加密卡。该卡采用性能价格比较高的DSP芯片实现加密算法的运算,利用PCI接口芯片、可编程逻辑芯片及Flash ROM等优化接口及逻辑设计。典型的分组密码加解密速度达Mbit/s,RSA加解密在数十Kbit/s以上。由于其通用、高速及价廉的特点,具有很好的实际应用前景,尤其适用于构建在广域网或Internet上的中小规模网络各主机间的信息交换与传输。

我要赚赏金

我要赚赏金