最近学习了一篇介绍芯海科技的高性能ADC设计的文章,感觉收获颇丰。特别是觉得其中有几个创新设计思路有一定的参考价值,列出来给和我一样的学习者分享下吧,有经验的高手们也可以出来点评一下:

一、高精度Sigma-Delta调制器

高精度ADC,特别是嵌入了处理器的SOC芯片,噪声模拟模型非常复杂,除了量化噪声及模拟部分各种器件的热噪声、1/f噪声外,还有数字电路随时钟节拍运作时产生的衬底噪声和电源噪声。这些噪声源都严重地影响了高精度Sigma-Delta 调制器的性能。为此,我们在模拟部分设计时,充分考虑了这些噪声的调制和成型,创新性地使用了四阶随机斩波Sigma-Delta调制器。

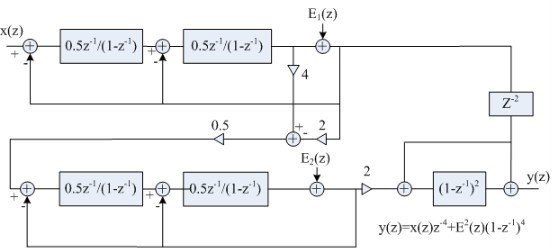

图: Casecode结构四阶Σ-Δ调制器Z域模型

从图中可以得到四阶Z域的传输函数为:

![]()

可以看出,经过这个调制器后,输入信号X(Z)没有什么变化,仅仅是增加了延迟,但是量化噪声被函数H(Z)=(1-Z-1)4所加权,成为高频成分,这个函数我们称为噪声成型函数。利用调制器后面的降采样滤波器,我们可以将高频部分(基带以外)的量化噪声滤除,这样我们就得到了信噪声比极高的量化信号。

二、高性能的DSP信号处理模块

高精度的ADC除了低噪声的模拟调制器外,高性能的DSP模块同样起着至关重要的作用。这个滤波器,既要保证足够高的信噪比,又要考虑系统对信号的延迟。现在的测量系统,通常都要求One Cycle Settle 即单周期建立。为此,我们必须采用先进行高速高阶滤波器,再加一阶滤波输出的方式,来同时达到高的性噪比和高的响应速度。

三 高性能PGA实现方式

由于高精度ADC所探测的信号非常微弱,必须要通过前置放大器对信号进行放大,提高信噪比。前置放大器在放大信号的同时,自身也会产生噪声,并且会限制系统的共模输入范围,增加系统成本及功耗。芯海科技采用了特有的低功耗、低噪声、低成本PGA实现方式,设计出了高性能的SOC方案,大大提高了产品的市场竞争力。

我要赚赏金

我要赚赏金