我目前是使用 一級一級 DFFE 去做 StateMachine

不是一般制式化的寫法

但是有問實際在做 IC Design 的工程師有提到

一般 Statemachine 還是要用制式化的寫法

要使用 parameter 宣告後,去做設計

不然以後若用到 有很多 state 要宣告的話…

你的 DFFE 連接就會有一堆

但是我覺得制式化的方式很麻煩,而且不彈性

請問,以各位的經驗,是否還是用制式化的方式去寫 會比較方便呢?

也許就像先前版主所述,以寫程式的方式來做,高階語言像C一樣

是比較彈性且方便的呢?

可否幫忙比較優缺點呢?

也許我該學習其他的設計方法!

共10条

1/1 1 跳转至页

StateMachine寫法!!

只看楼主 1楼

关键词: StateMachine 寫法

2楼

我的写法是:

先parameter所有状态

然后 分 三段式来写 FSM:组合逻辑写状态转换规律、时序逻辑写CurState<=NextState、组合逻辑写每个状态下的操作

5楼

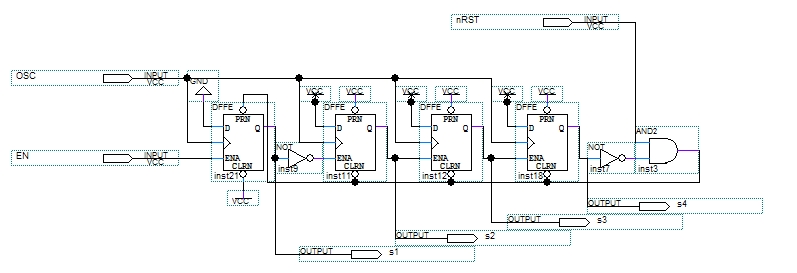

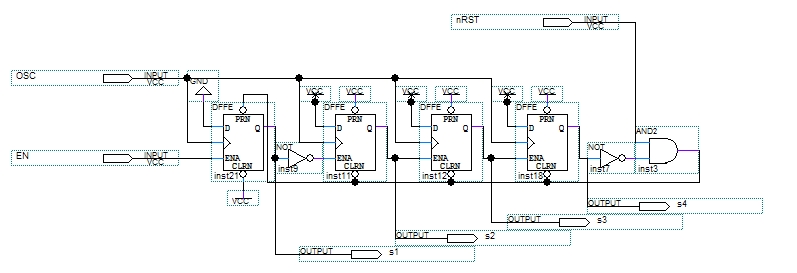

我的方式如下… 以4個State為例…畫圖較容易解釋!我覺得這樣的方式完全可以直接使用,而且 timing 較不易有問題!且變化很大…亦可在 enable 每個 state 的 前端,加入很多判斷式!重點:不用宣告,想用就用,想多加個 state 就再加入一個 DFFE 即可

6楼

当设计很简单时DFFE当然可以,如果复杂的话,就很麻烦了。而且画图的,移植不方便。

没有parameter的话,我想过了一两个月自己都看不明白了。可读性太差,不利于阅读、修改,不便于项目传承。

就像不会有人愿意去阅读别人写的汇编代码一样。

在项目组中,规范的写法往往比细节技巧更重要

没有parameter的话,我想过了一两个月自己都看不明白了。可读性太差,不利于阅读、修改,不便于项目传承。

就像不会有人愿意去阅读别人写的汇编代码一样。

在项目组中,规范的写法往往比细节技巧更重要

8楼

畫圖是較容易了解,就好像是架構圖,用來講解就很容易懂

實際的設計當然還是用寫 code 的方式,因為要轉換不用供應商的 FPGA

一般寫完 code ,可讀性也不是很好

只有看架構圖,才能夠完全了解 這個 設計是在做什麼

所以,以我的設計,除了 source code 以外,我都會再做一個 架構圖

一個是好了解,一個是介紹就容易懂

因為再怎麼說,有圖的講解,比用講解 source code 的方式易懂

因為也 trace 過別人的 code ,也知道要看別人的 code 不容易

只能看完 code 後,再手畫出自己了解的架構,整體來看才知道每個電路連接為何

當然,也可以用 debussy 去看連接圖,但我覺得若是 trace 別人的設計

還是要自己將架構圖畫出來,才有辦法全部都了解!

複雜的設計,也是要 bottom to top 方式設計

不可能一開始就設計到很複雜的電路

即然是由小到大的設計

就可以一個 block 接一個 block ,我認為這也是可以克服的!

所以,以圖來看的話,就很直觀,不用再一行一行的去看 code

一般看到 code 就投降輸一半了

哪還看得下去呢!…所以,一定要有圖來輔助,才能事半功倍!

實際的設計當然還是用寫 code 的方式,因為要轉換不用供應商的 FPGA

一般寫完 code ,可讀性也不是很好

只有看架構圖,才能夠完全了解 這個 設計是在做什麼

所以,以我的設計,除了 source code 以外,我都會再做一個 架構圖

一個是好了解,一個是介紹就容易懂

因為再怎麼說,有圖的講解,比用講解 source code 的方式易懂

因為也 trace 過別人的 code ,也知道要看別人的 code 不容易

只能看完 code 後,再手畫出自己了解的架構,整體來看才知道每個電路連接為何

當然,也可以用 debussy 去看連接圖,但我覺得若是 trace 別人的設計

還是要自己將架構圖畫出來,才有辦法全部都了解!

複雜的設計,也是要 bottom to top 方式設計

不可能一開始就設計到很複雜的電路

即然是由小到大的設計

就可以一個 block 接一個 block ,我認為這也是可以克服的!

所以,以圖來看的話,就很直觀,不用再一行一行的去看 code

一般看到 code 就投降輸一半了

哪還看得下去呢!…所以,一定要有圖來輔助,才能事半功倍!

9楼

做设计,画框图是必然的,但也只能是简单的框图,信号流程图。

然后用CODE从行为上去描述。

要Trace项目,仅有Code当然不行,还要有相应的文档。

所以软件的定义才是CODE+文档

然后用CODE从行为上去描述。

要Trace项目,仅有Code当然不行,还要有相应的文档。

所以软件的定义才是CODE+文档

共10条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |