嵌入式微控制器对复杂程度各异的多种应用而言都很普遍。赛灵思 (Xilinx)自2000年以来始终致力于推出固化的(PowerPC® 405 和 PowerPC 440)以及基于构造 (MicroBlaze™) 的嵌入式微处理器。MicroBlaze 的显著优势在于能满足复杂应用的需求,有些情况下除了运行简单的通用应用而外还能运行操作系统。

设计人员能够在当前所有的赛灵思架构中实施 MicroBlaze 软处理器,在不同产品系列间实现方便的转换,获得无与伦比的灵活性。但是,MicroBlaze系统设计不仅要在70多种参数中选择,而且还要借助一系列功能强大的嵌入式工具,如果应用只需要简单的微控制器,那么这种设计方法可能反倒不实用了。

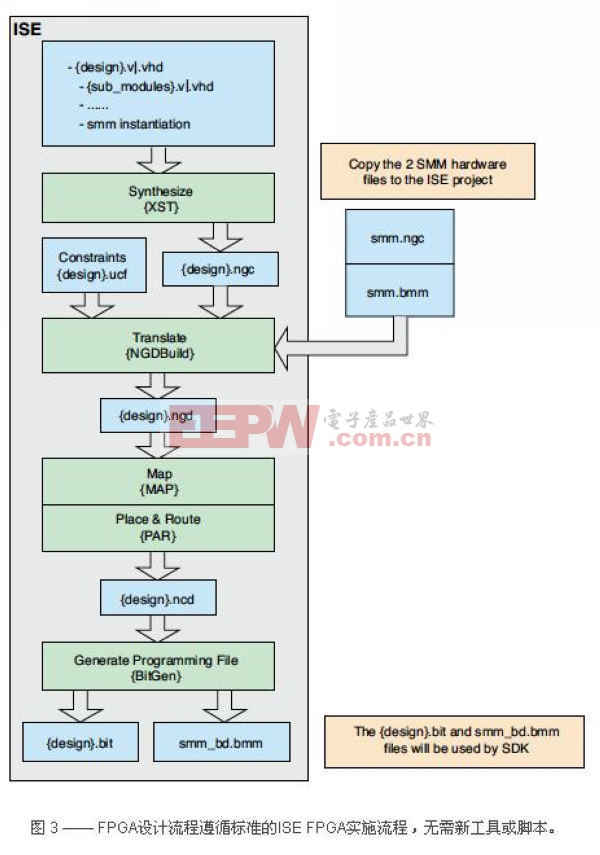

但是,利用适当的技术,用户可以开发构造简单的预配置MicroBlaze微控制器,并方便快捷地将其添加到任何FPGA设计中。可将控制器的实例直接加入HDL。用户能在标准的FPGA设计流程中直接使用,无需特殊的脚本或复杂的步骤。仅需三个文件即可启动设计工作,包括两个硬件实施文件和一个软件定义文件。这种方法使工程师不用学习或者只需很少量的学习就能快速启动FPGA嵌入式设计工作。

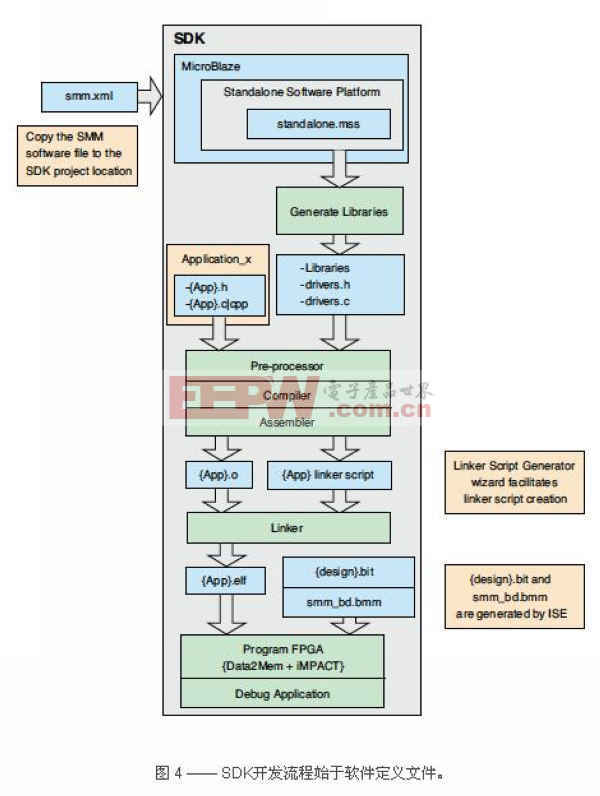

在ISE® 11.1中启动MicroBlaze软件开发工作,可使用独立的软件开发套件 (SDK) 进行C和C++应用的创建和调试,而无需全面的嵌入式开发套件(EDK)。

微控制器预配置了两种选项,UART和调试。表1显示了根据微控制器配置不同而给出的各种FPGA系列的尺寸估算值。此外,Virtex®器件使用了两个Block RAM,而Spartan®器件使用四个Block RAM。对应用代码进行调试后,用户即可移除调试选项,以减小控制器的尺寸。例如,Spartan-6微控制器仅需要220个切片。

微控制器概览

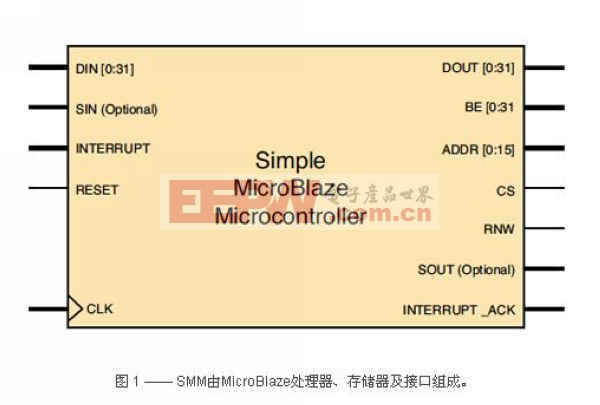

简单MicroBlaze微控制器包含的组件有32位MicroBlaze处理器、8KB RAM/ROM、带64KB寻址空间的32位用户接口、中断支持、可选UART以及可选的JTAG调试接口。图1显示了系统方框图。

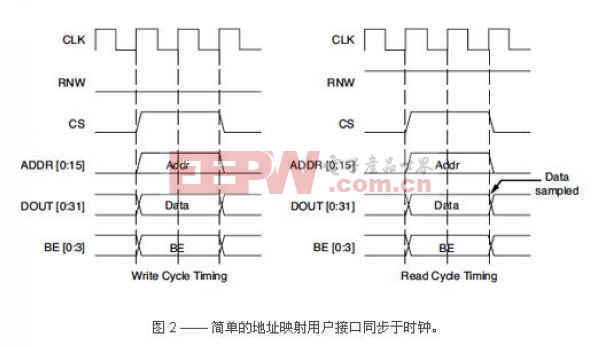

根据需要以及实施工具允许的范围,时钟输入可高可低。有效高电平复位输入与输入时钟内部同步。中断输入信号可提供中断支持,微控制器提供服务时用中断确认输出进行确认。此外,简单的地址映射用户接口也同步于时钟,支持用户定制。图2显示了用户接口的时序。可将字节启用用于字节和半字事务处理。

我要赚赏金

我要赚赏金