工程师在设计过程中,经常需要一定的创造力(你不妨称之为数字管道胶带)才能够保证设计的顺利完成。过去8年时间里,我曾经目睹许多优秀工程师利用这一方法出色地完成了许多工作,而他们采用的最主要工具就是 FPGA Editor。

利用FPGA Editor,你可以察看完成的设计并确定是否在FPGA构造一级真正实现了设计意图 – 而这对于任何工程师或现场应用工程师来说都是非常需要的。假设你拿到协作者的设计,需要对其进行修改,但他们的 HDL源代码非常难于理解,或者根本没有任何注释或文档。也许你只是想将某些时钟逻辑锁定,但却不知道实例的名称或者如何将其锁在所希望的位置。下面讨论的一些用来探查FPGA构造以及创建命令行补丁的技巧可以帮助设计人员满足不断迫近的任务期限要求。

FPGA构造勘察技巧

当赛灵思发布针对新FPGA器件的工具时,通常我做的第一件事就是打开FPGA Editor来勘FPGA器件的内部构造。具体做法是找到 Xilinx →ISE →Accessories菜单并点击FPGA Editor图标,或者在命令行键入 fpga_editor。 图形用户界面打开后,在File菜单下选择New。FPGA Editor会询问设计文件名称和物理约束文件。此时还没有任何设计文件,因此随便键入一个设计文件名(例如,test.ncd),并选择希望察看的器件类型。 FPGA Editor将会使用同样的名字作为物理约束文件的名称,并加载一个空白设计。

另一种方法是编译随软件提供的某个ISE®工具套件设计例子,并将其加载到FPGA Editor中来察看FPGA构造。加载一个设计实例可以显示更多细节,并且更容易定位感兴趣的项目。

在FPGA Editor中浏览只需要记住两件事:

1、 如何利用CTRL/Shift快捷键进行放大缩小。

2、 如果利用F11键放大选定的项目。不使用GUI按钮快速缩放的方法是,按住Ctrl和Shift键,然后分别利用鼠标左键和右键进入放大和缩小。要想快速找到任何项目,在GUI右上角的列表窗口(List window)中选择该项目即可。一旦定位了想找的项目,按F11键。阵列窗口(Array window)就会放大显示该项目。

FPGA Editor有四个主要窗口:列表(List)、全局(World)、阵列(Array)和块(Block)。List窗口显示设计中所有活动的项目。通过此窗口顶部的下拉菜单可选择其内容 – 列表内容包括已经布局或还未使用的部件、网络或未布线的网络等等。

全局视图窗口(World Windows)始终显示完整FPGA硅片视图,这在试图确定某个网络的布线情况时非常有用。同时,阵列窗口(Array window)则是FPGA构造和逻辑的动态视图。如果双击Array视图中的任何项目,会显示Block视图,给出所选择项目或逻辑单元的详细情况。

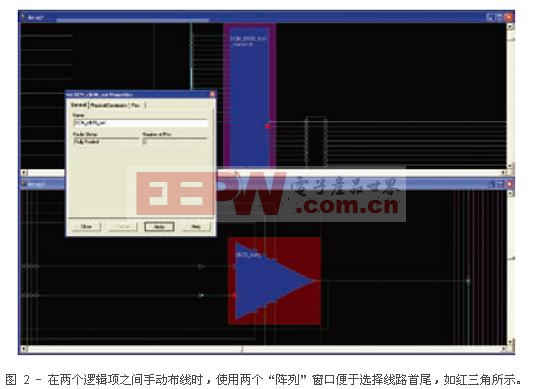

为方便浏览或对设计进行编辑,这些窗口可以复制。许多情况下,打开第二个Array窗口会比较方便同时在设计的两个不同部分工作。例如,假设需要在全局时钟缓冲器和芯片底部的触发器之间增加一条布线。如果在一个Array窗口中显示全局时钟缓冲器的输出,另一个Array窗口则显示触发器时钟输入,那么会做起来会更方便。不然的话就必须来回缩放来定位布线的两端,显然这很繁琐。

在FPGA Editor GUI的右侧是一组由20个功能按钮组成的工具条,用于设计察看和编辑。通过编辑 $XILINX/data目录下的 fpga_editor.ini文件可以增加更多功能按钮。当察看设计时,应当随时使用INFO按钮。该功能会将所选择项目的所有信息转录到控制台(Console)窗口。这一功能非常方便,你可以在控制台窗口中标注数据并将其拷贝到其它地

方使用,例如编写UCF约束。

一旦了解了最基本的概念和操作,就可以开始察看FPGA构造。通常我都从时钟逻辑开始。这包括数字时钟管理器(DCM)、锁相环(PLL)、全局时钟缓冲器(BUFG)、区域时钟缓冲器(BUFR)、I/O缓冲器(BUFIO)以及不同的时钟区域。(要想按字母列出项目表,可以到LIST窗口点击Type来排序。)点击一个DCM并按F11。ARRAY窗口会定位到选择的DCM并放大显示它。继续点击DCM并观察GUI底部的Console窗口,其中会显示与下面类似的内容:

comp “DCM_BASE_inst_star”, site

“DCM_ADV_X0Y9”, type = DCM_ADV

(RPM grid X73Y202)

这是有用的数据。 拷贝并粘贴上述内容到UCF文件中,并作如下更改以锁定这一DCM逻辑:

INST “DCM_BASE_inst_star”

LOC=DCM_ADV_X0Y9;

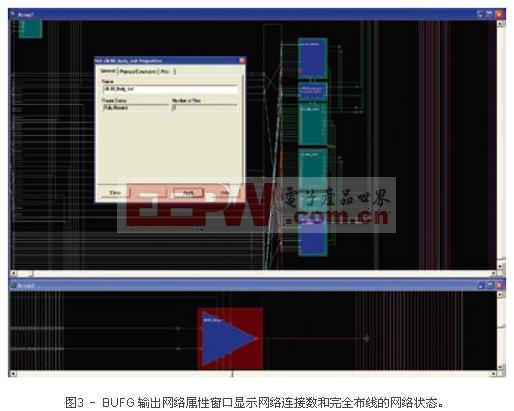

利用这一方法,几乎可以锁定FPGA中的任何项目。 下面是BUFG锁定的另一个例子:

c o m p “ B U F G _ i n s t _ s t a r ” , s i t e

“BUFGCTRL_X0Y20”, type = BUFG

(RPM grid X73Y124)

INST “BUFG_inst_star”

LOC=BUFGCTRL_X0Y20;

再次回到 List 窗口并标注同一DCM。 双击之后将会在Block视图中显示该DCM以及所有设置和参数。这是一项非常强大的功能,可用于FPGA构造中的任何逻辑项目。如果选择一个逻辑片并双击它,就可以看到逻辑片是如何布线连接的,以及是否使用了进位链或本地触发器。

我要赚赏金

我要赚赏金