`timescale 1ns / 1ps

module s2p(clk, clk_div2, reset, x, b_i, b_q);

input clk;

input clk_div2;

input reset;

input x; //用0代表“1”,1代表“-1”

output b_i, b_q;

reg b_i, b_q;

reg [1:0] x_t, d_t; //用于计算差分编码

wire d_x; //差分输出信号

always @(posedge clk) begin

if(!reset) begin

x_t <= 0;

d_t <= 0;

end

else begin

x_t[1:0] <= {x_t[0], x};

d_t[1:0] <= {d_t[0], d_x};

end

end

// 完成差分预编码, d_x(n) = x(n)*x(n-1),等效于求异或

assign d_x = (x_t==2'b11) ? 0 :(x_t==2'b00) ? 0 : 1;

// 产生分流的I、Q信号

reg s_flag; //符号标志

always @(posedge clk) begin

if(!reset) begin

s_flag <= 0;

b_i <= 0;

b_q <= 0;

end

else begin

if(d_t[1] == d_t[0])

s_flag <= s_flag;

else

if(clk_div2)

s_flag <= !s_flag;

else

s_flag <= s_flag;

if(clk_div2) //完成符号修改

b_i <= s_flag;

else

b_q <= s_flag ^ d_t[1];

end

end

endmodule

简单的测试程序

`timescale 1ns/1ps

`include "./s2p.v"

module s2p_tb;

reg clk,clk_div2,reset,x;

wire b_i, b_q,d_x,x_t,d_t;

s2p MM(.clk(clk),

.clk_div2(clk_div2),

.reset(reset),

.x(x),

.b_i(b_i),

.b_q(b_q));

initial

begin

clk=0;

clk_div2=0;

reset =0;

# 40 reset = 1;

x=0;

# 20 x=0;

# 20 x=0;

# 20 x=0;

#20 x=0;

#20 x=1;

#20 x=1;

#20 x=0;

#20 x=1;

#20 x=0;

#20 x=0;

#20 x=1;

#20 x=1;

end

always #10 clk=~clk;

always #20 clk_div2=~clk_div2;

endmodule

问题如下:

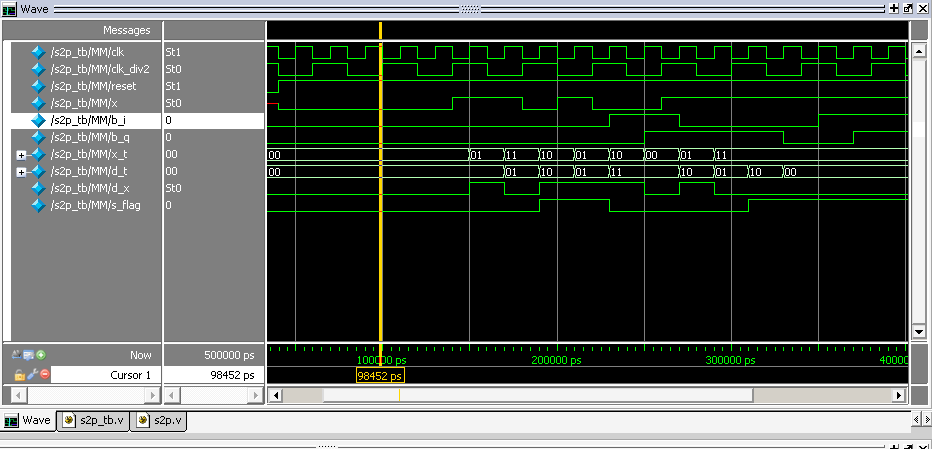

差分后d_x为00000100011101对吧?

正常思路下,i、q两路信号值如下:

d_i:0000111(书上结果000011000011)位数怎么多了,而且和仿真出来的图也对不上,图和书上一样的。

d_q:001010(书上结果00001111001)

但是仿真后的结果不是这个,而且和书上给的结果也不一样,但图是一样的,还望那位大侠给点指导。

难道差分变换还有别的方式?

数目《无线通信的MATALB和FPGA实现》西瑞克斯那本MSK调制部分,160页。

他这个程序是对的,但结果让人匪夷所思,求解答。特别是里面有句话的理解不到位:“经串并转换后变成两路并行不归零码,且相互差一个Tb。”这个Tb是在查分时候差出来的还是在串并转换查出来的。他这个串并转换不是2位一截断,求真相,谢谢。

我要赚赏金

我要赚赏金