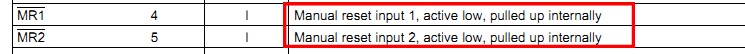

外部上拉是可以提高驱动能力,那内部上拉呢?看dsp、电源很多引脚都有该功能;

此外,DSP中还提及,因为有内部上拉,故GPIO口可选择进行输入、输出、高阻态三种情况的能力。是因为OD或OC门加内部上拉形成的?

共9条

1/1 1 跳转至页

7楼

有内部上拉是可以简化设计,一般来说有内上拉的除非特别说明,都可以悬空处理。主要上下拉就是为了防止输入口因为电平不确定而带来的错误配置。所以一旦有了内部若上下拉。就避免了这个问题

共9条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |