入门的第一个:间隔点亮LED。

分配管脚有点被教程里的图片小小误导了一下的感觉,

好在暂时还是成功了:编译、下载。

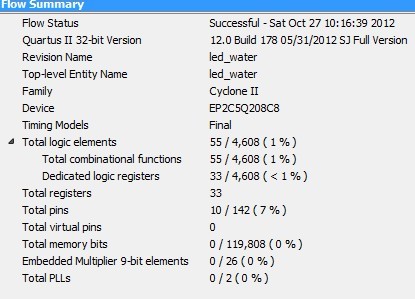

编译的结果最后一行提示:

Info (293000): Quartus II Full Compilation was successful. 0 errors, 15 warnings

总结一下,今天只是比昨天多试了下:管脚配置,编译。

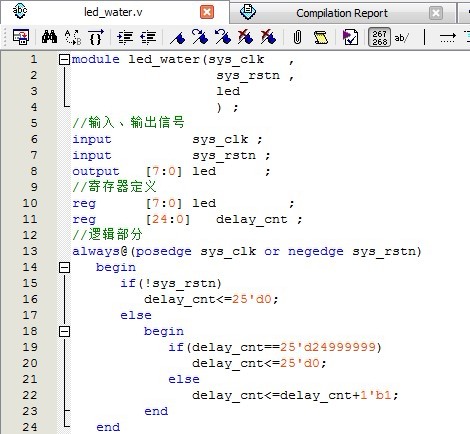

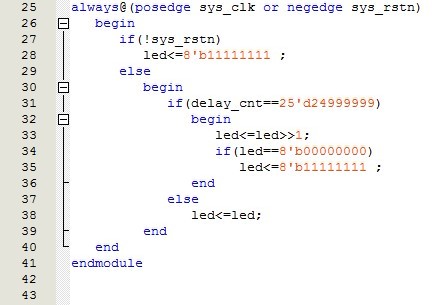

参照“FPGA入门系列实验教程——流水灯”,学习;

编译,下载,再修改,再来...

(主要需要修改:管脚配置、LED驱动电平不同、时钟输入)

管脚配置花了比较多的时间,操作不熟练

在教程里,还可以学到配置管脚的好办法,啸风整理的那份脚本子这里大大的有用啦。

与前有进步,开始用上时钟了(clk)

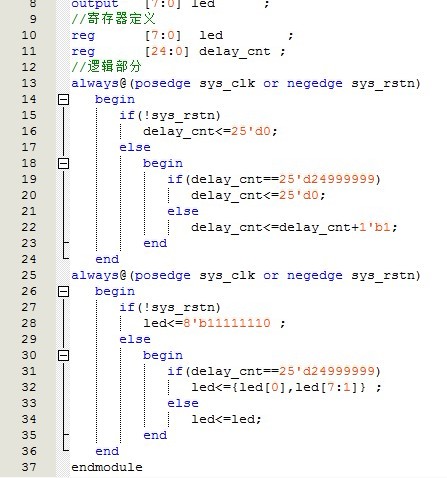

【代码】

module ledwater(clk,led);

output [7:0] led;

input clk;

reg[8:0] led_out;

reg[8:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==9'b000000000)

led_out=9'b111111111;

led_out1=~led_out;

end

end

assign led=led_out[7:0];

endmodule

【视频】

编译,下载,再修改,再来...

(主要需要修改:管脚配置、LED驱动电平不同、时钟输入)

管脚配置花了比较多的时间,操作不熟练

在教程里,还可以学到配置管脚的好办法,啸风整理的那份脚本子这里大大的有用啦。

与前有进步,开始用上时钟了(clk)

【代码】

module ledwater(clk,led);

output [7:0] led;

input clk;

reg[8:0] led_out;

reg[8:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==9'b000000000)

led_out=9'b111111111;

led_out1=~led_out;

end

end

assign led=led_out[7:0];

endmodule

【视频】

继11位流水后,小改一下就了跑马啦:

module ledwater(clk,led);

output [10:0] led;

input clk;

reg[11:0] led_out;

reg[11:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+2'b10;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==12'b000000000000)

led_out=12'b000000000001;

led_out1=~led_out;

end

end

assign led=led_out1[10:0]; //

endmodule

【视频】

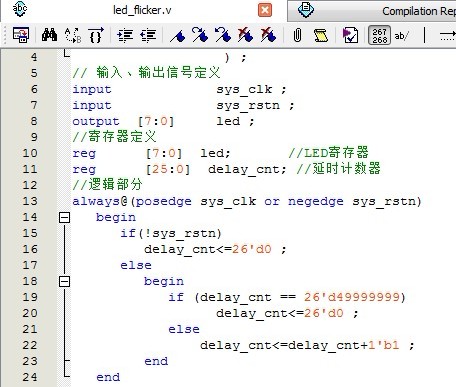

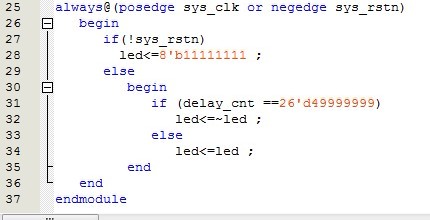

第一时间下载学习 手把手教你学习FPGA—LED篇

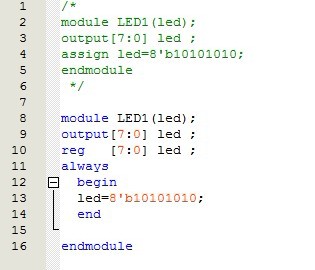

【LED亮灯】

我的练习截图(2个都试了,下面是其中的1个):

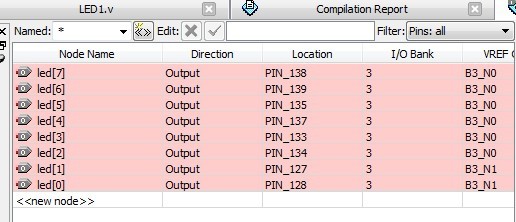

保存的文件名:LED1.V

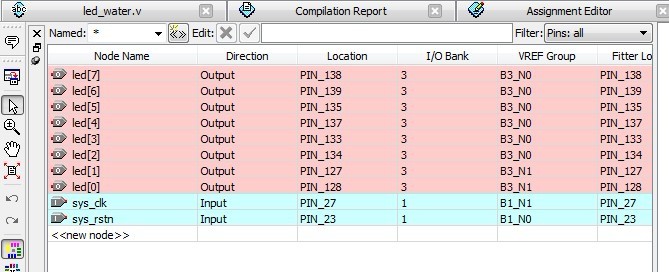

手工分配管脚:

正确的结果:

曾经出现错误的结果,数码管都是亮的;后把未用管脚设为3态输入,就好了。

刚开始感觉分配管脚比较麻烦,还经常找不到地方(管脚、修改的地方),现在慢慢习惯了。

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |