在DE2的开发板中,有两块RAM,一块8MB的SDRAM和一块512K的SRAM,在SOPC中有SDRAM的IP核,而对于SRAM则没有,今天参照网上的一个例子将IP核自己定制了下,测试成功了。

module SRAM_16Bit_512K(

input csi_clk,

input csi_reset_n,

input [17 :0] avs_address,

input [1:0] avs_byteenable_n,

input avs_write_n,

input [15 :0] avs_writedata,

input avs_read_n,

output [15 :0] avs_readdata,

inout [15 :0] coe_SRAM_DQ,

// SRAM Data bus 16 Bits

output [17 :0] coe_SRAM_ADDR,

// SRAM Address bus 18 Bits

output coe_SRAM_LB_N,

// SRAM Low-byte Data Mask

output coe_SRAM_UB_N,

// SRAM High-byte Data Mask

output coe_SRAM_CE_N,

// SRAM Chip chipselect

output coe_SRAM_OE_N,

// SRAM Output chipselect

output coe_SRAM_WE_N

// SRAM Write chipselect

);

assign coe_SRAM_DQ = coe_SRAM_WE_N ? 'hz : avs_writedata;

assign avs_readdata = coe_SRAM_DQ;

assign coe_SRAM_ADDR = avs_address;

assign coe_SRAM_WE_N = avs_write_n;

assign coe_SRAM_OE_N = avs_read_n;

assign coe_SRAM_CE_N = avs_read_n & avs_write_n;

assign {coe_SRAM_UB_N, coe_SRAM_LB_N} = avs_byteenable_n;

endmodule

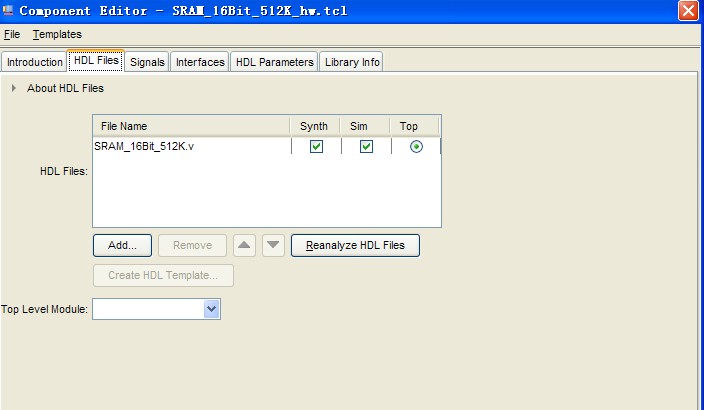

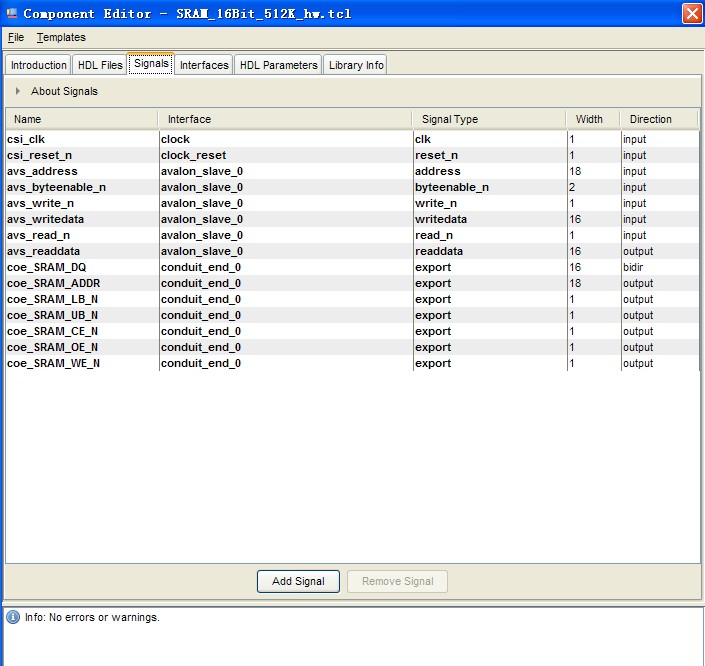

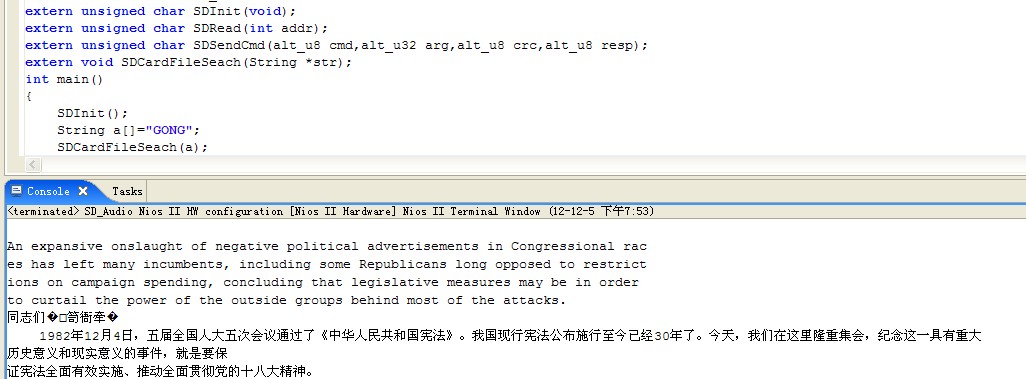

这是V文件的代码,然后在NIOS中点击File->New component选择中间的HDL Files

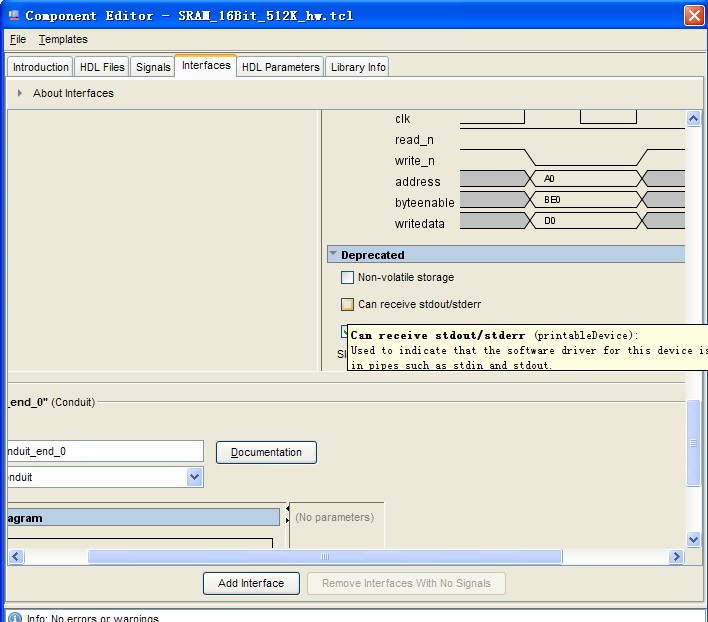

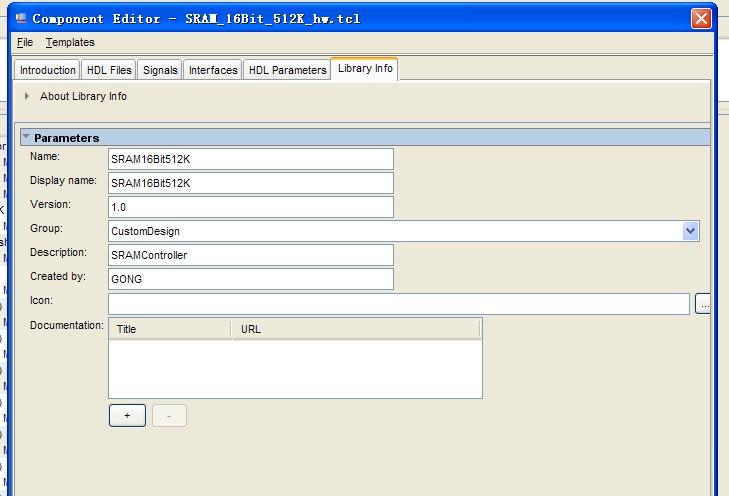

接着:

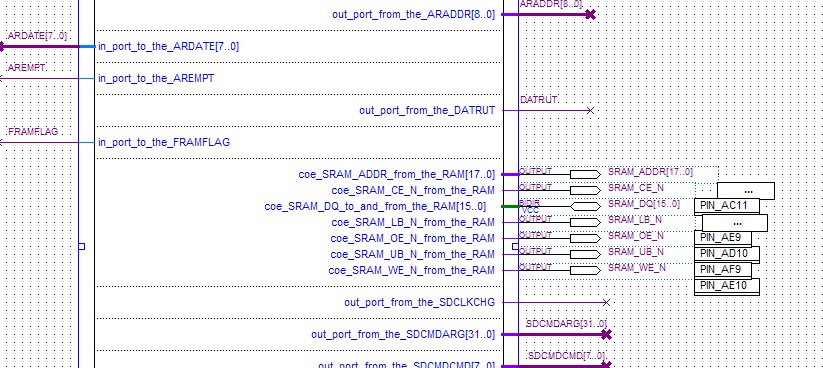

这样子在SOPC中就可以看到IP核了,然后在NIOS中进行测试成功。

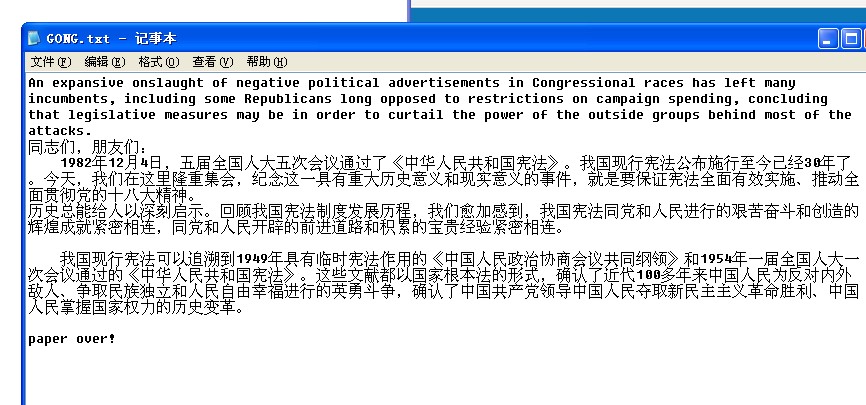

这是我的软核的图,因为我要适用SDRAM当做图像的缓存区进行显示,因此在这里就适用SRAM做软核的RAM。进行的SD数据的读取,最后读取成功。

我要赚赏金

我要赚赏金