作者:北方工业大学 梁方舟 李金泉 黄训磊

指导教师:王玉花

作品简介

一.开发背景

传统的频率特性测试仪(扫频仪)中幅值检波电路采用模拟电路实现如二极管包络检波电路,存在测量精度低,不能数字显示峰值的缺点。为此设计了一个基于可编程逻辑器件的数字系统实现峰值检波。

二.结构说明

系统构成:模拟数字转换(A/D)及前端信号处理模块电路、XILINX公司的FPGA最小系统板(型号DIGILENT BASYS2),电源电路及测试用信号源和示波器。

三.功能

系统可以测量被测模拟信号的峰值,峰值用8个LED显示,同时用8段数码管将其以十进制的格式显示。

四.使用说明

被测信号(实验时采用信号发生器)加到电路输入端ADIN,按下复位键,设计的系统检测电压的峰值,以二进制的格式用8个LED显示出来。同时用8段数码管将其以十进制的格式显示出来。如显示结果从左到右每位的单位为1V,100mV,10mV。

对不同的测试信号如光信号、热信号、压力信号、位移信号、速度信号、气敏信号等需要增加电路转换为电信号,才可检测峰值。

设计说明

一.设计方案

以FPGA开发板Xilinx Spartan-3E为控制核心,8位的极高速A/D转换芯片TLC5510为数据采集外设,以及Xilinx ISE硬件设计开发工具为基础制作峰值检波电路。

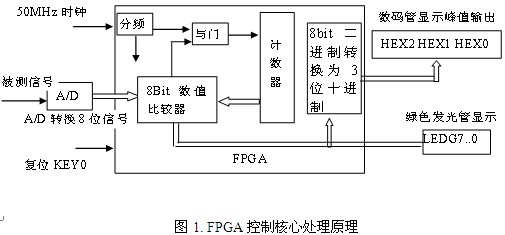

设计峰值检波电路,其中分频电路、比较器、与门和计数器及8位二进制数转换为3位十进制数的电路由FPGA实现,下载工程到Xilinx Spartan-3E开发板。

1)假设由Xilinx Spartan-3E开发板的8个拨码开关SW7---SW0提供A/D转换后的8bit并行输出信号。

2)时钟:Xilinx Spartan-3E板50MHz晶振;

3)复位按键:KEY0 ;

采用三位七段数码管显示十进制峰值。

采用A/D 8位并行输出器件采集被测信号峰值,输出8bit并行转换信号到FPGA输入端,当A/D转换信号大于计数器的计数值,数值比较器的输出为高电平,与门导通,时钟被送到计数器的时钟输入端,计数器开始计数,当计数器的计数值大于A/D转换信号值,数值比较器输出为低电平,封锁与门,计数器停止计数,输出被测信号的峰值。

二.设计原理

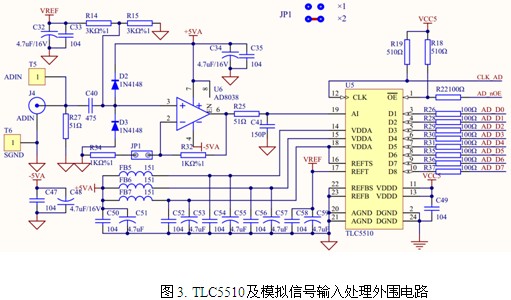

TLC5510为具有AD和DA的双功能芯片。其AD部分具有快速的转换速度,接口为同步并行8位接口,因此接口实现简单。该芯片最高可以使用20MHz同步时钟。

AD同步时钟设计为12.5MHz。因此AD的采样率(Vsample)为:

![]()

根据采样定理分析可知,无损还原信号最大频率为6.25MHz,则输入信号的频率最大仅能为6.25MHz的频率信号。

TLC5510的参考电压Vref为4.0V,由于其为8位,则其AD的分辨率(LSB)为:

其精度达到了十毫伏级,可以灵活应对大部分传感器的灵敏度。

为实现测量的实用性和普遍性,AD外围电路采用正偏压设计,使-2.0V~+2.0V输入信号皆可测量。考虑到Vref=4.0V,所以正偏压为2.0V。采用如下的电路结构,就可以实现对信号的+2.0V偏移。

在FPGA开发平台上,通过软件编程,完成对晶振的分频,以供TLC5510使用。

峰值检波部分,采用本次的AD[0]:AD[7]与上次采集的AD[0]:AD[7]相比,若上次的数据大于本次的数据,则不进行数据处理;否则将本次的比值以二进制的方式控制8个发光二极管指示数值,并转换为十进制,通过运算,在四位8段数码管上显示采集到的具体电压值(![]() )。

)。

首先用一个A/D转换器,将模拟电信号转换为位数字信号;再用一个比较器将转换的数字信号与设定的初始最小值进行比较。当转换的数字信号大于初始值时输出高电平给与门。与门输入端接时钟计数信号(时钟由50MHZ的晶振供应)和比较器的输出端。与门输出接计数器。当比较器输出高电平时,计数器开始根据时钟计数,再通过比较器将计数值与信号比较。直到计数器的值等于信号值,比较器输出低电平将与门锁死计数器停止计数,得到输入信号的峰值。再通过发光二极管将峰值以二进制的格式显示出来,并应用8段数码管,将峰值以十进制的格式显示。

TLC5510采用了半闪速结构及CMOS工艺,因而大大减少了器件中比较器的数量,而且在高速转换的同时能够保持较低的功耗。在推荐工作条件下,TLC5510的功耗仅为130mW。由于TLC5510不仅具有高速的A/D转换功能,而且还带有内部采样保持电路,从而大大简化了外围电路的设计;同时,由于其内部带有了标准分压电阻,因而可以从+5V的电源获得2V满刻度的基准电压。

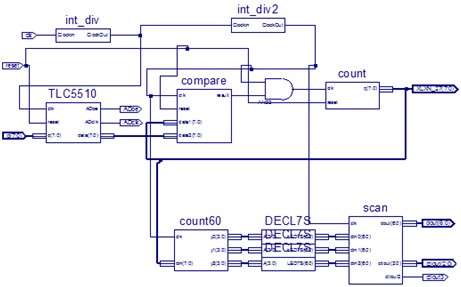

软件设计在ISE10.1环境下开发,采用VHDL语言描述编程。顶层设计文件如图4.

作品特色

采用数字系统比传统的模拟电路实现方法具有精度高、方便数字显示的优点,采用FPGA方便以后更改设计和电路升级。

该电路设计可以用于数字频率特性仪等需要精确测量信号峰值并数字显示的环境。

系统演示视频:http://v.eepw.com.cn/video/play/id/2356

我要赚赏金

我要赚赏金