关键是电路分割要合理,这样就不必分离接地层,如图9所示。注意,如果布局允许您将电路保持在各自区域内,便不需要分离接地层。如此分割可提供星型接地,从而将返回电流局限在特定电路部分。

例如,受尺寸限制的影响,电路板无法实现良好的布局分割时,就需要分离接地层。这可能是为了符合传统设计要求或尺寸,必须将脏乱的总线电源或高噪声数字电路放在某些区域。这种情况下,分离接地层是实现良好性能的关键。然而,为使整体设计有效,必须在电路板的某个地方通过一个电桥或连接点将这些接地层连在一起。因此,应将连接点均匀地分布在分离的接地层上。

最终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低或强行将返回电流耦合至敏感电路的最佳位置。如果此连接点位于转换器、其附近或下方,则不需要分离接地。

结束语

由于最佳选项太多,布局考虑总是令人困惑。技术和原则一直是公司设计文化的一部分。工程师喜欢借鉴以前设计中的经验,同时产品上市压力使设计人员不愿更改或尝试新技术。他们拘泥于风险权衡,直至系统内出现重大问题。

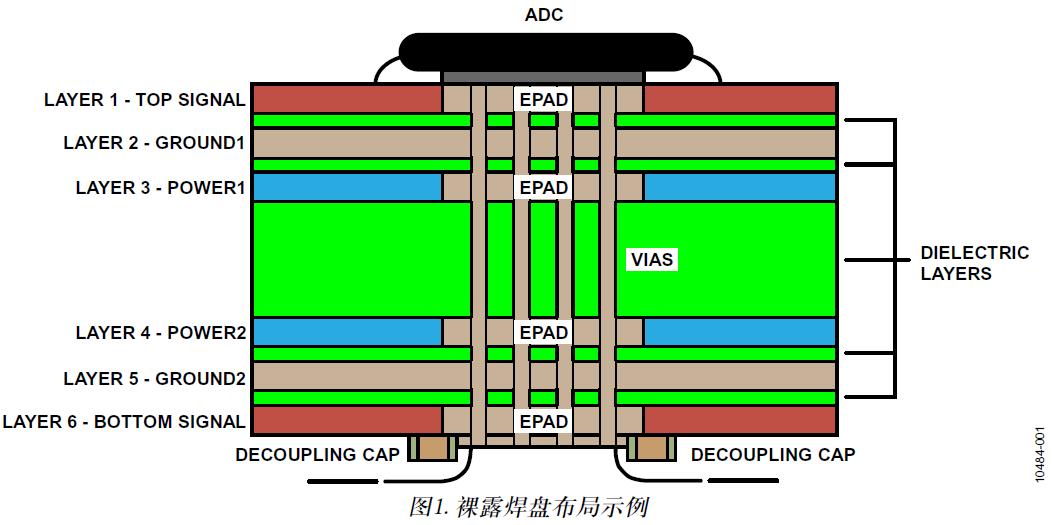

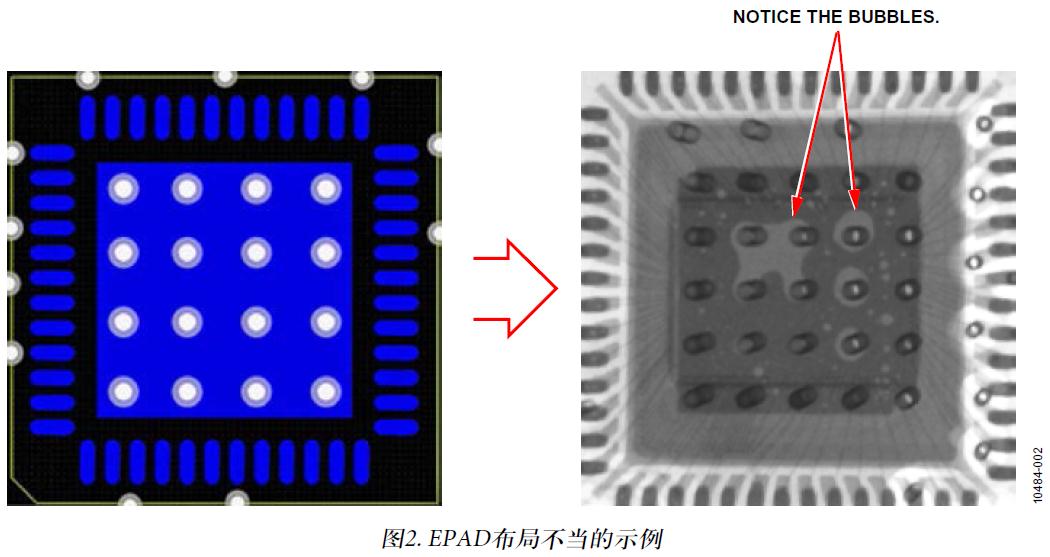

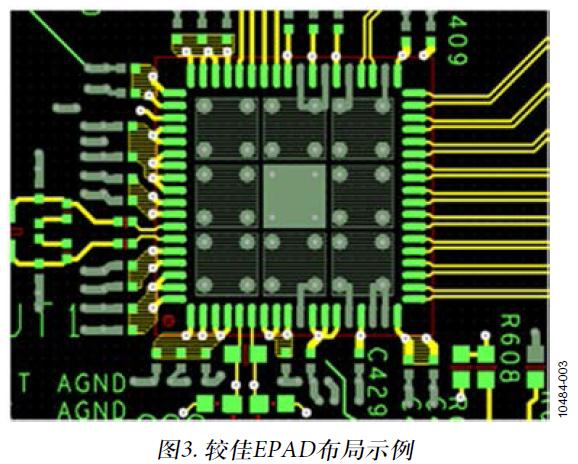

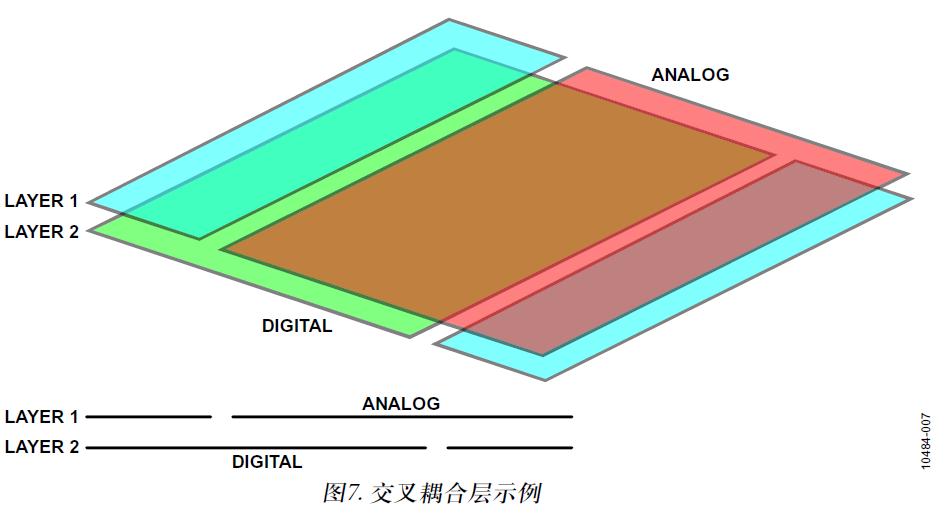

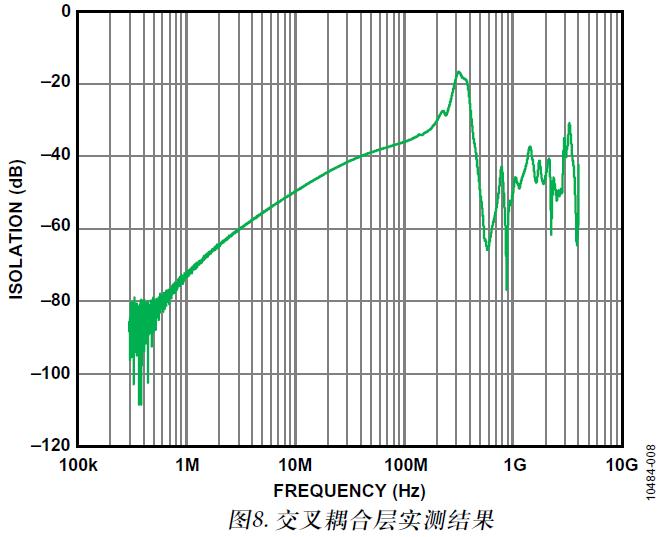

在评估板、模块和系统级别,简单的单一接地最佳。良好的电路分割是关键。这也影响到层和相邻层布局。如果敏感层在高噪声数字层以上,请注意可能会发生交叉耦合。组装也很重要;提供给PCB车间或组装车间的制造笔记应善加利用,确保IC裸露焊盘和PCB之间具有可靠连接。

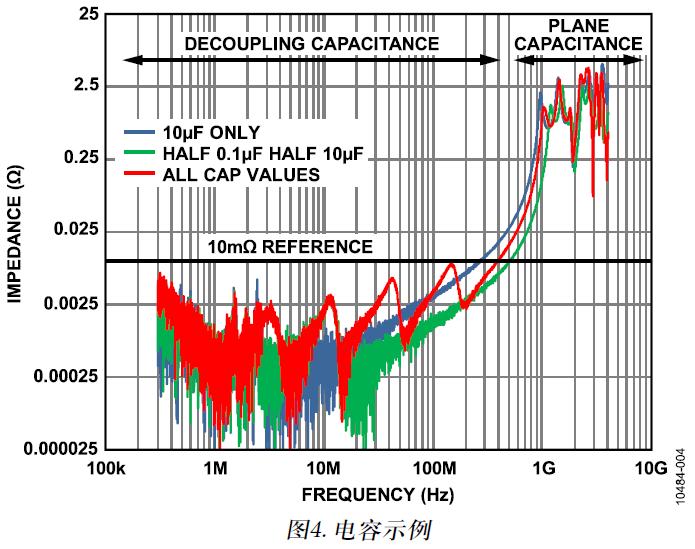

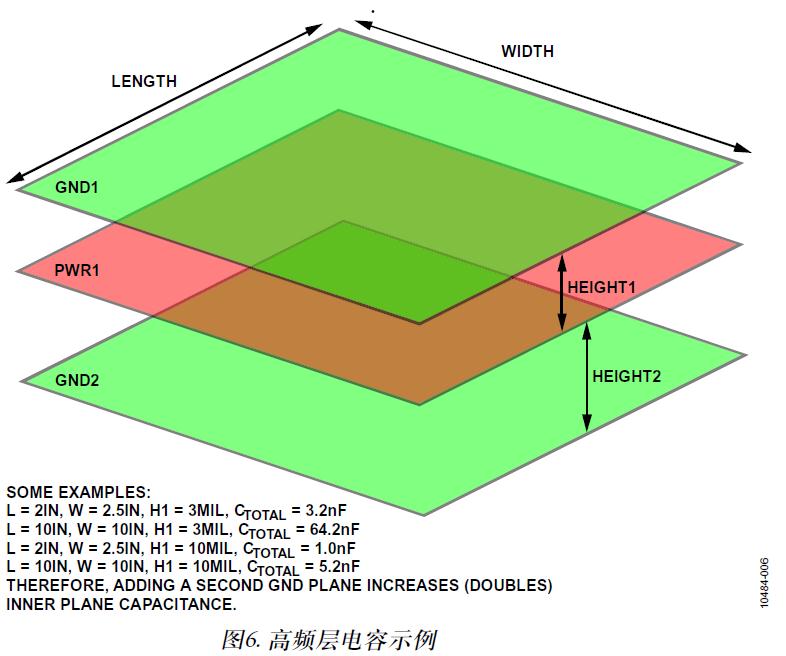

组装不良常常导致系统性能欠佳。靠近电源层入口点和转换器或IC的VDD引脚的去耦总是有利的。然而,为了增加固有高频去耦电容,应使用紧密叠置的电源和接地层(间距4密尔)。此方法不会带来额外成本,只需花几分钟更新PCB制造笔记。

设计高速、高分辨率转换器布局时,很难照顾到所有的具体特性。每个应用都是独一无二的。希望本应用笔记所述的几个要点有助于设计工程师更好地了解未来的系统设计。

参考文献

Gri�n, Gary. 2006. AN-772 Application Note, A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP).

Kester, Walt. 2004. Analog-Digital Conversion: Seminar Series Analog Devices, ISBN 0-916550-27-3. (Also available as The Data Conversion Handbook, 2005, Elsevier/Newnes,ISBN 0-7506-7841-0)

我要赚赏金

我要赚赏金