读书是一种心态,分享是一种快乐

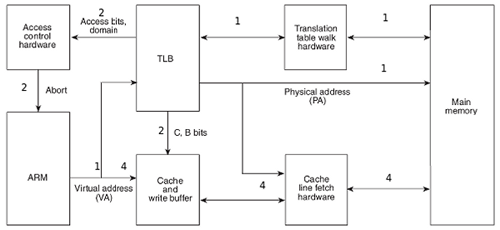

说到arm处理器,就得说说MMU即内存管理单元,在arm处理器中它包含在CP15协处理器中。

当然CP15协处理器中有16个寄存器,具体的功能自己看文档吧,

http://pan.baidu.com/share/link?shareid=468376&uk=3708539847 ,

这篇文档的名字arm architecture reference manual,ps:英文的!

主要说下,CP15协处理器的register 2:Translation table base。

这个寄存器存储的是,页表在内存中基地址,这个寄存器存储的也就是个物理地址。

TLB是mmu的一部分,它是一种高速缓存,相当于cpu中的Icache,Dcache。

它缓存最近查找过的VA对应的页表项,为的是减少去访问物理内存的次数。

关于TLB,这是维基百科给的定义:

A translation lookaside buffer (TLB) is a cache that memory management hardware uses to improvevirtual

address translation speed. All current desktop, laptop, and server processors use a TLB to map virtual and

physical address spaces, and it is nearly always present in any hardware which utilizes virtual memory.

The TLB is typically implemented as content-addressable memory (CAM) .

The CAM search key is the virtual address and the search result is a physical address. If the requested ad

dress is present in the TLB, the CAM search yields a match quickly and the retrieved physical address can

be used to access memory. This is called a TLB hit. If the requested address is not in the TLB, it is a miss,

and the translation proceeds by looking up the page table in a process called a page walk. The page walk

is an expensive process, as it involves reading the contents of multiple memory locations and using them

to compute the physical address. After the physical address is determined by the page walk, the virtual a

ddress to physical address mapping is entered into the TLB.

在arm中没有像intel x86中io地址的概念,因为它的物理地址和io地址是统一编址,这样就是用统一的命令来对io口和物理内存进行访问了!!

我要赚赏金

我要赚赏金