我选择第二种方案:申请PCB板,购买组委会提供的元器件包

实验概要:

作为一种新兴的数码产品,数码相框由于其显示功能丰富、画质清晰、操作简单和携带方便等特点在人们的日常生活中得到了越来越广泛的应用。目前,市场上的数码相框大多是以ARM为核心的嵌入式系统,采用LCD作为显示屏。我希望通过本次“CPLD DIY”活动实现 基于CPLD的数码相框嵌入式系统。

完成功能:

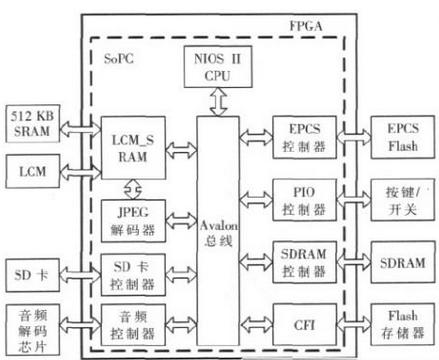

SD卡作为文件存储介质,用于存放音频与图像文件,编写SD卡控制器对SD卡进行读写控制;采用LCM显示屏作为数码相框的显示界面,SRAM作为LCM的显示缓存,存储图像数据供LCM刷新,并由LCM_SRAM IP核控制图像的显示;SDRAM为Nios II软核程序运行空间;EPCS对FPGA进行配置;Flash用来存储软件代码和数据。

关注这个CPLD的DIY很久了,以前学过的51,虽说有一定的编程基础,但Verilog HDL是初次接触,想通过贵网站的DIY活动实现这个实验,能熟练掌握CPLD对各种外设、总线的操作。自己的方向是高速数据采集,也想为以后的FPGA学习打下基础。希望我能从这次活动中有所收获。

我要赚赏金

我要赚赏金