,已经发了ADF4002,AD9516-3的配置,还有一个AD9523的配置,,过几天发咯!

这几天还在扫尾,待我稍作整理

嘿嘿,

http://forum.eepw.com.cn/thread/228366/1 AD9516-3配置

http://forum.eepw.com.cn/thread/228363/1 ADF4002配置

AD9523是ADI公司生产的低功耗、多路输出时钟分配芯片,旨在满足LTE和多载波GSM基站设计的时钟要求。它依靠外部VCXO清除参考抖动,以满足严格的低相位噪声要求[7]。

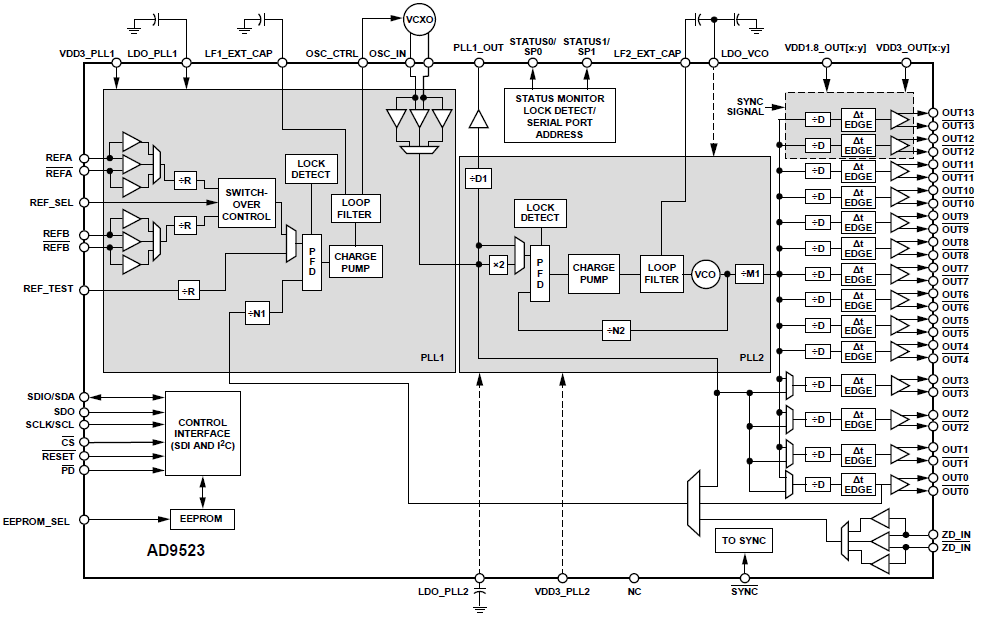

AD9523的系统结构图如 图 所示,内含集成锁相环(PLL)和电压控制振荡器(VCO)。片内调谐频率范围3.6Ghz到4.0GHz,有两对差分参考时钟输入端,可选择其中一个或者两个作为参考时钟,为了降低因参考时钟噪声带来的干扰,AD9523内部含有两个PFD,第一个PFD的输出控制电荷泵的输出电压的大小,电荷泵的输出端经过环路滤波器之后,控制VCXO输出一个频率稳定,噪声较低的信号,该信号将作为第二个PFD的输入。

AD9523的输出频率从1Mhz到1Ghz,具有14路输出,可配置为LVPECL、LVDS、HSTL或LVCMOS模式,同时每一路输出均可编程配置延迟,还具有一个非易失性EEPROM存储配置设置,可以从非易失性EEPROM中配置芯片,也可以通过SPI方式配置芯片。当参考时钟是差分输入时,最大输入频率为400Mhz,当参考时钟是CMOS单端输入时,最大输入频率为250MHz。

AD9523的配置同AD9516-3相似都是四线的串行控制,四线分别为CS(芯片选择)、SCLK(串行时钟信号)、SDIO(串行数据输入\输出)、SDO(串行数据输出)。

1. 配置PLL1相关寄存器(0x010~0x01D)

2. 配置PLL2相关寄存器(0x0F0~0x0F6)

3. 配置输出端口相关寄存器(0x190~0x1BB)

4. 配置状态输出寄存器(0x230~0x232)

5. 配置电源控制模块(0x233)

6. 配置0x234(更新所有寄存器)

在配置时,尽量不要使用软件复位信号,使用硬件复位信号

示列代码

——回复可见内容——

AD9523

AD9523

我要赚赏金

我要赚赏金