因为主板和说明文件很全,焊接对于大家来说没什么困难,所以直接开始说焊接后的注意事项

来和大家交流一下。

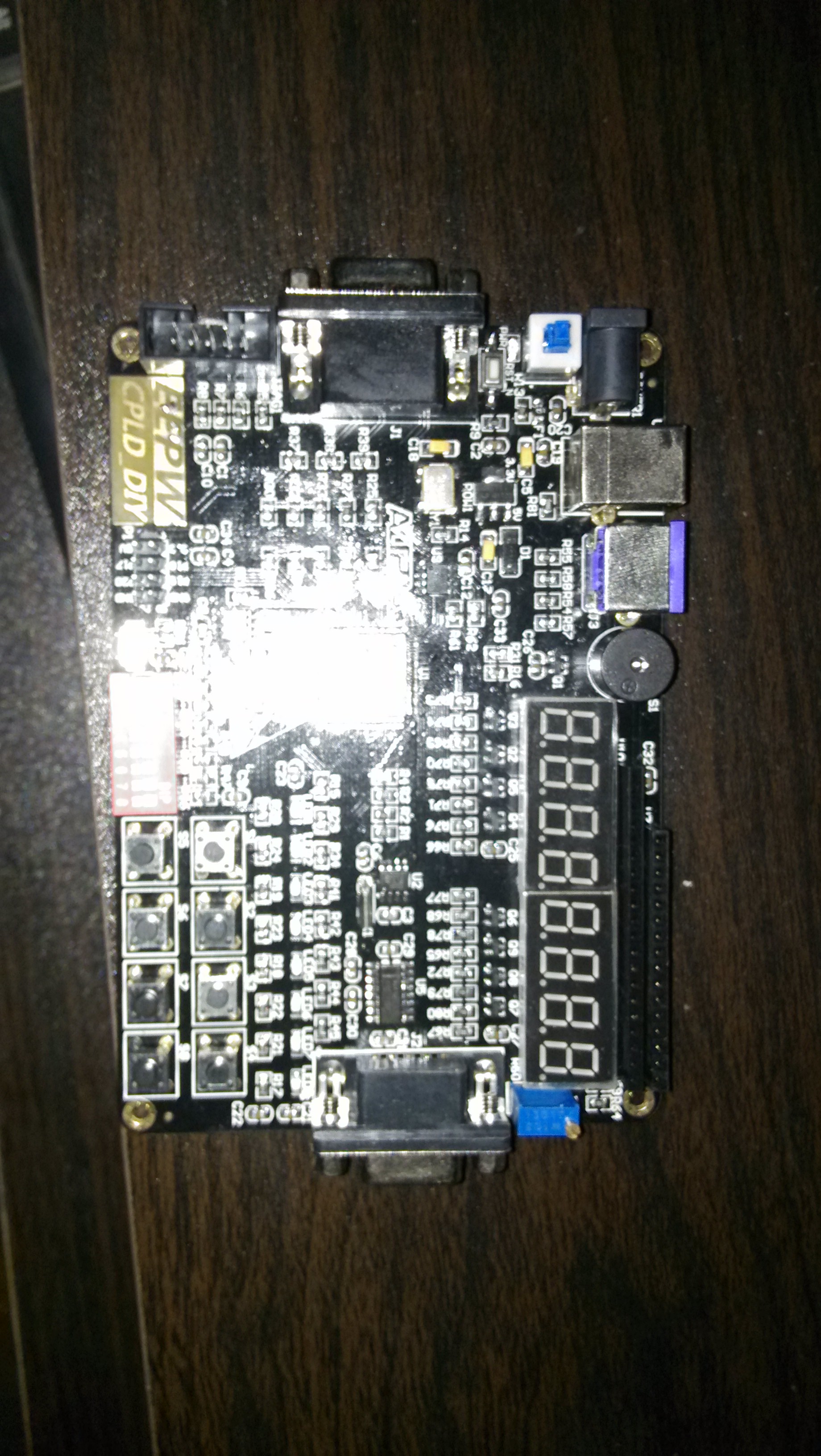

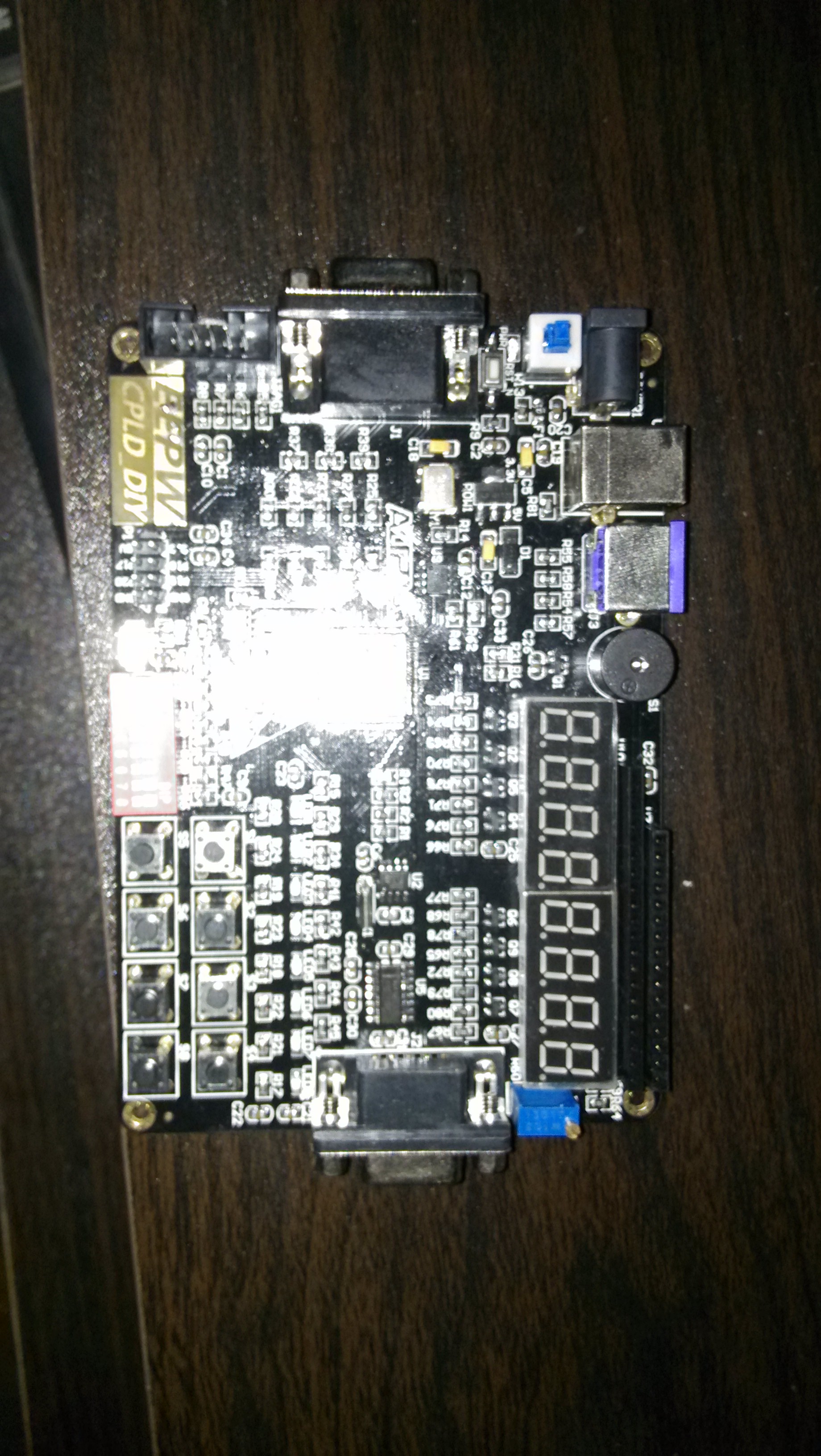

1.上主板图

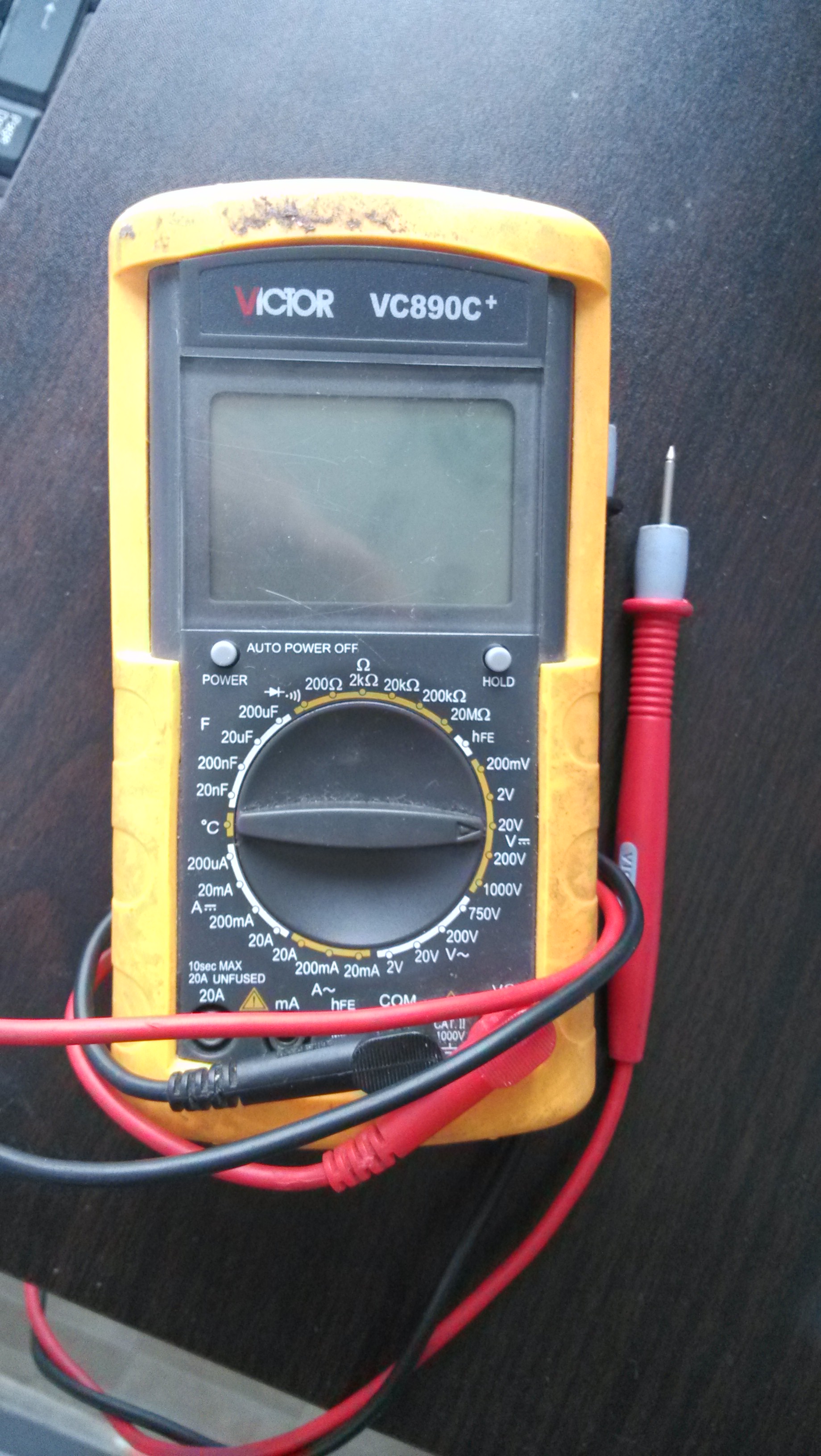

2.焊接完毕后先用肉眼检查一下主板上IC,电阻和电容等元器件的pin是否有短路,冷焊,虚焊,漏焊等现象

3.使用万用表打到欧姆档量测5V和3.3V对地阻值,如果在100以内或者只有几欧姆,甚至是0欧,这时候你需要注意了。不要着急上电。再次检查一下是否有焊接短路或者元器件焊接反了或者不匹配。

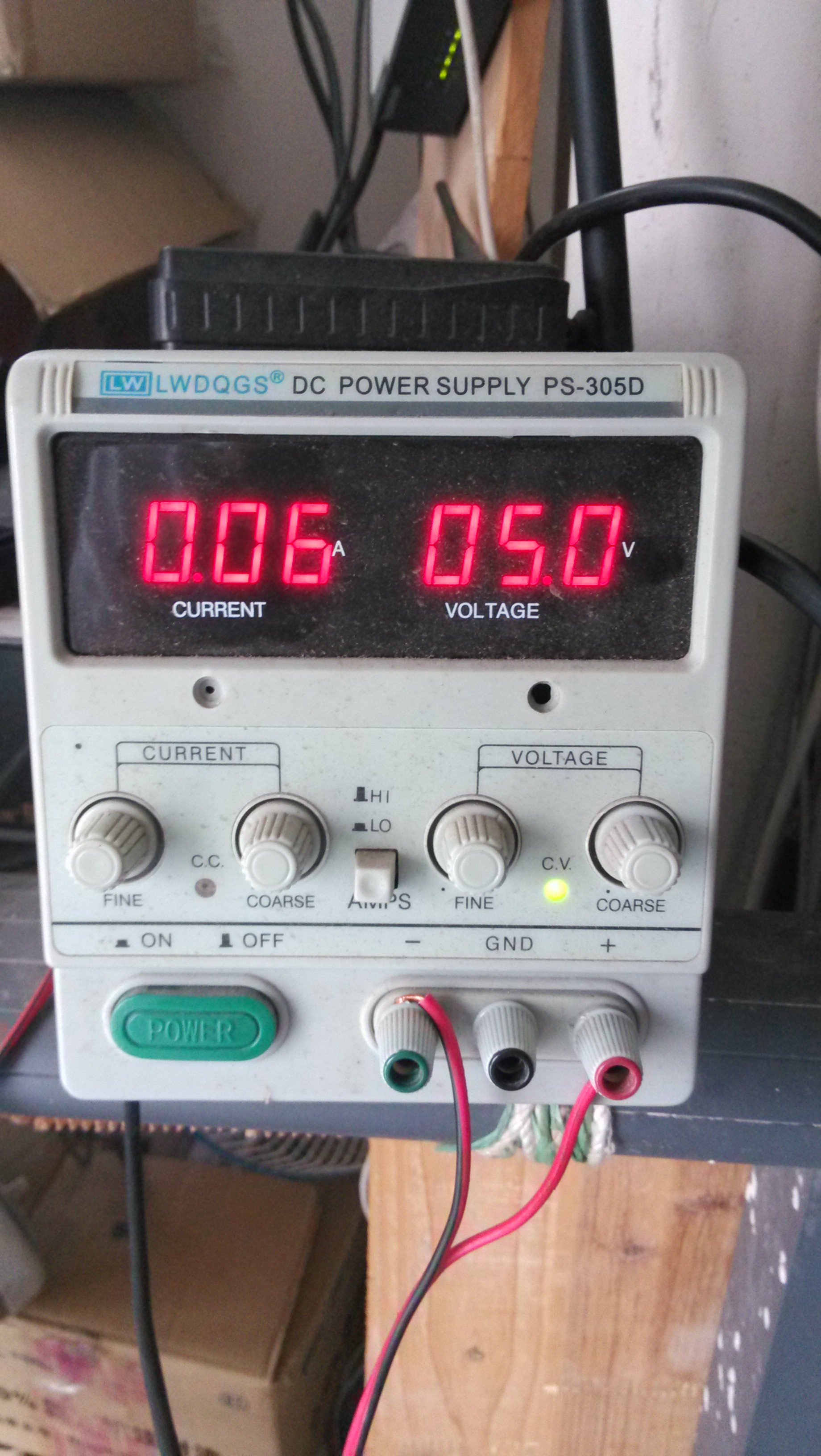

4.以上检查无问题将可调电源电压调至5V,电流输出调制0A,避免上电烧板。上电后慢慢调节电流旋钮,如果电流超过70mA这时候你需要注意了,如果显示100mA那么你就需要断电检查主板了。我这边上电量测的电流为60mA。

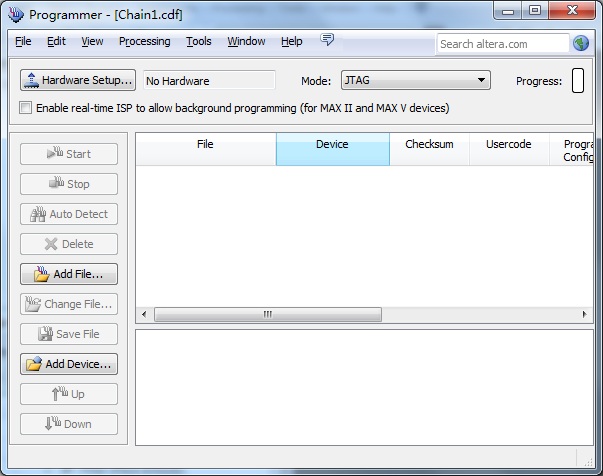

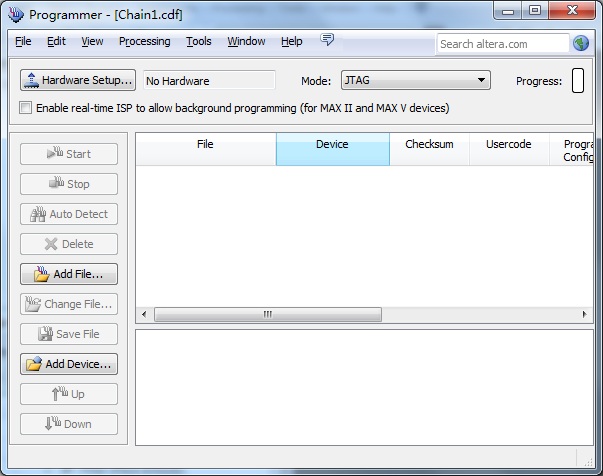

5.上电后连接usb-blaster,打开Quartus II,选择Tool->Progarmmer,弹出烧写程序的对话框。

点击Hardware setup 选择USB-blaster,然后点击add file选择提供的四个例程。然后右侧框出来文件信息,你可以点击文件名字后面的复选框。勾选前三组即可。点击start进行刷写。

6.刷写后会遇到LED数码管显示的不是“7654321”是乱码,这是你的主板元件引脚没有焊接好检查下。我的是有细小锡线短路。庆幸的是IO引脚没有烧掉;烧写按键程序1~7按键有按下去唔蜂鸣器的声音,检查发现CPLD引脚未焊接好。用手用力按压CPLD,同时按压按键就可以发出声音。重新加锡焊接。

刷写四个固件完毕,未发现异常。准备写个demo让蜂鸣器响代码。

我要赚赏金

我要赚赏金