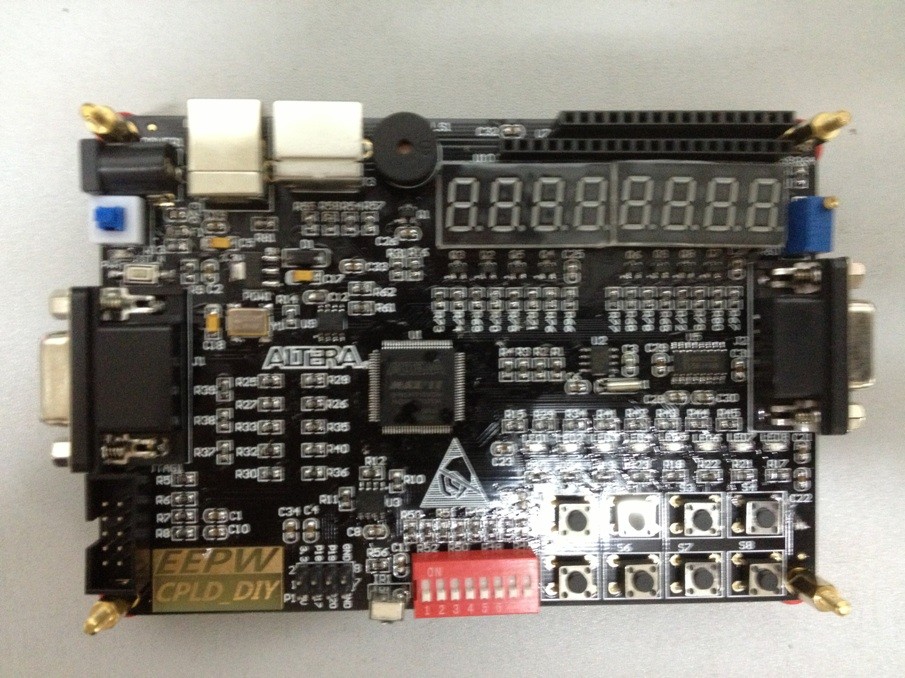

6.25号收到板子和器件包,周末焊接完成,各种忙,迟上加迟啊,先上照片,看一下板子,稍后上进程细节。。。

时间:2013年9月19日

实验:LED闪烁 1S间隔(手把手教程对应的课后作业);

进程: 此间一直在学习Verilog语言,由于基础为零,只是理解CPLD的原理而已,至于开始一个设计,哪怕是小小的简单的,也不知道该如何下手,例如,FPGA开发当中仿真是非常重要的,那么每个工程都要进行仿真吗?最简单的点灯程序写好了,怎么分配管脚?我的Pin Planer打开了怎么看不到有待分配的管脚定义呢?一头雾水,初学者大概都有此类问题,每个问题都去坛子里群里问吧,那自己就没有什么思考了,而且,已经入门的高手大都享受过这样的进阶乐趣了,怎能在百忙中回答这些琐碎问题。自己来吧还是,绝知此事要躬行啊!

我首先看了教程中的例程,再三琢磨,终于明白了,算是看懂了吧,然后新建立一个工程,原样敲进去例程,编译、通过(必须啊,抄的啊这是),然后分配管脚,处理未使用管脚(容易忘哦这一点),然后下载,完成后立即观察到8只LED按照同样频率(0.5S周期)闪烁,欣喜!!

按照课后作业要求,使8只LED间隔1S闪烁,easy!于是我改了代码,如下:(稍等,记得有规则说此处不能上源码?而且我用手机拍照的,现在还没传到电脑上)。

要实现1S间隔闪烁,只需要让计数器计数到50M即可,外部晶振50M赫兹,也就是每秒计数50M次,那么这样的频率正是所要的。于是直接修改了计数寄存器的值为49 000 000,然后,编译,下载,就等1S闪烁了,结果,竟然闪烁的更快了!?什么情况呢,计数大了,反倒闪烁快了,难道是要缩小计数值??仔细看了代码,没错啊,计数大才能获得更长的周期啊,然后。。。终于想到,计数寄存器位宽设为25为,那么最大值是335 544 32,到不了49 000 000啊,原来如此,增加一位位宽,编译,下载,终于实现了,闹钟正在桌子上哦,闪烁节奏,正是秒针的节奏,就是这个了!

module led_flick(sys_clk,sys_rstn,led);

input sys_clk;

input sys_rstn;

output [7:0] led;

reg [7:0] led;

reg [25:0] delay_cnt;

always @(posedge sys_clk or negedge sys_rstn)

begin

if (!sys_rstn)

delay_cnt <= 26'd0;

else

begin

if (delay_cnt==26'd49999999)

delay_cnt<=26'd0;

else

delay_cnt<=delay_cnt+1'b1;

end

end

always @ (posedge sys_clk or negedge sys_rstn)

begin

if (!sys_rstn)

led <= 8'b11111111;

else

begin

if (delay_cnt==26'd49999999)

led=~led;

else

led=led;

end

end

endmodule

享受进步的快乐!

这可全得感谢CPLD DIY活动啊,这可还得感谢EEPW啊,珍惜这个活动,继续进行下一进程!

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |