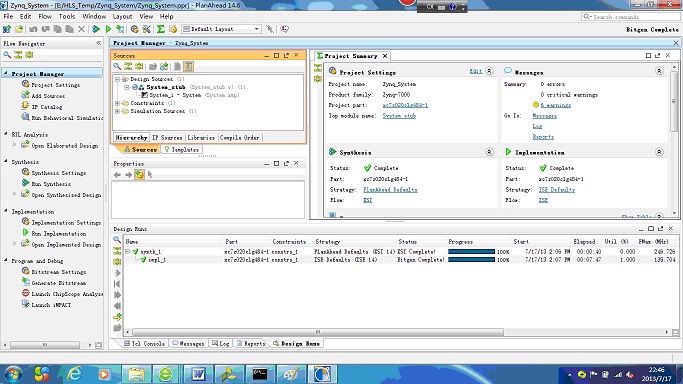

1. 拿到zingboard板时,发现没有光盘资料,随后科通技术支持email了部分资料,其中原理图很有用,感觉zing就是xc702的翻版。Xilinx的东西只在10.1时接触过,没有实际项目中用过,心想既然要学习,就用最新的vivado2013.2,到xilinx上注册下载,居然老是出错,无法下载,最后求助nakey,用其账号下了最新版,看来xilinx对我不友好呀,嫌我们一直用altera? 打开vivado,界面操作功能和planAhead太像了:

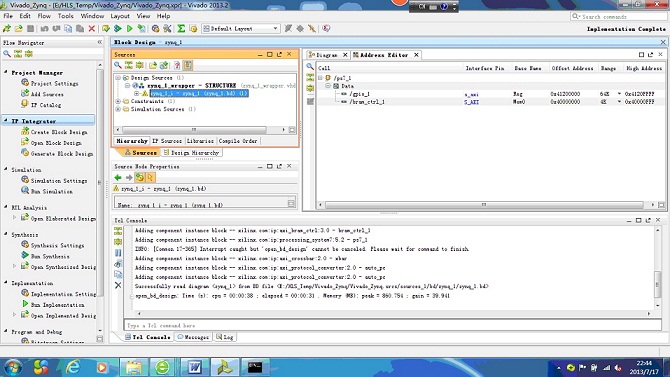

图vivado

图 planAhead

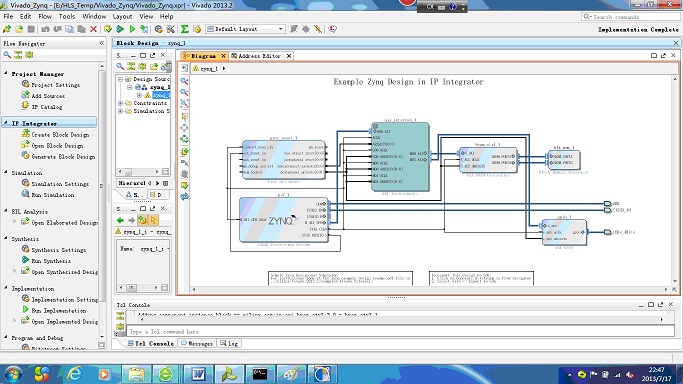

按planAhead的用法,试着在vivado中做了个简单系统,想测试看看:

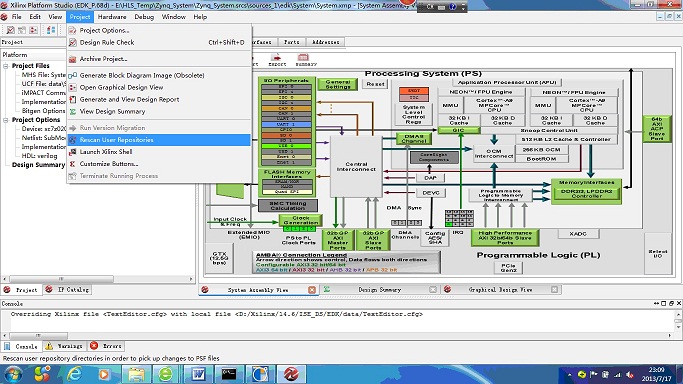

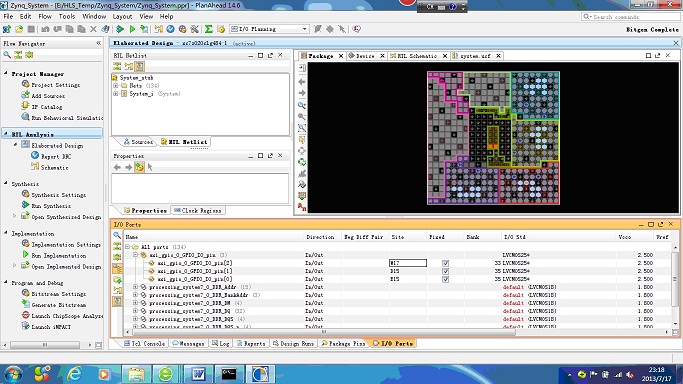

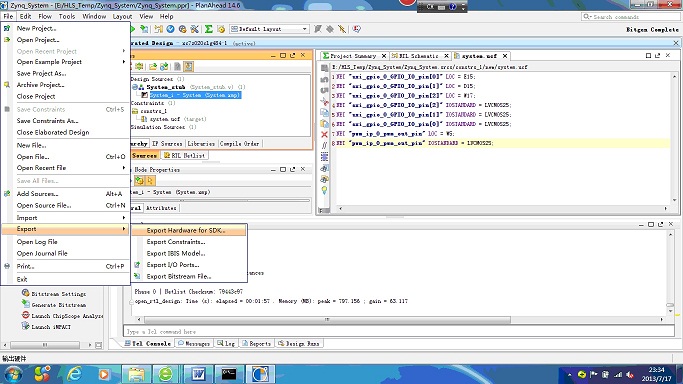

各步执行很慢,在最后生成bitstream时居然死机了,发现电脑内存用尽了,我电脑是win7/4G内存,不甘心,电脑复位后,将什么360等所有不用软件全部退出,再经过很长时间最后成功生成bitstream,感觉vivado比planAhead更耗费资源。因此,还是先在planAhead下构建zynq,首先构建个基本zynq,外带EMIO(MIO引脚固定,相对简单),EMIO的引脚是外扩到PL部分的,而不是直接由PS的引脚输出,刚好zing的W5, W17, D15 ,E15外接了led,故将EMIO设为3位分别从W17,D15,E15输出,pwm_out接W5:

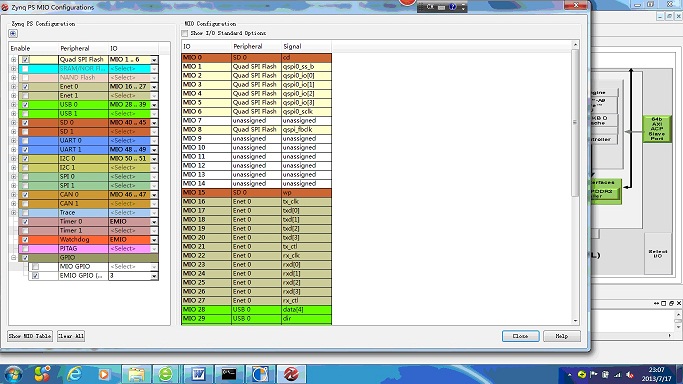

下图是在XPS中配置EMIO

图一

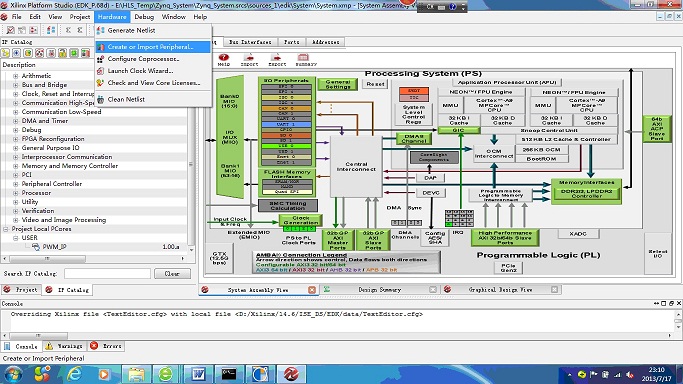

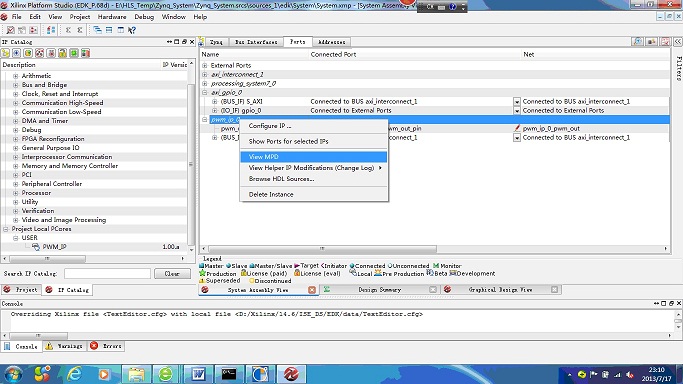

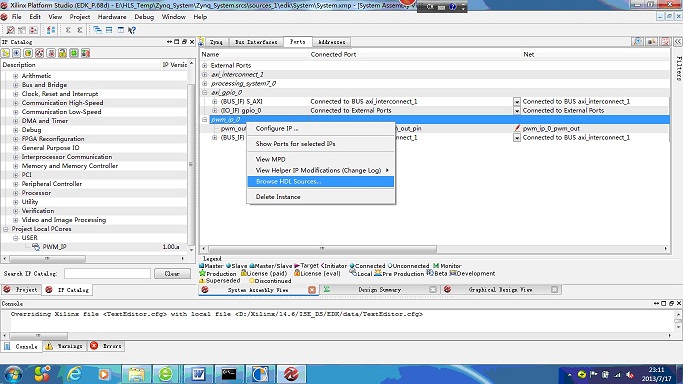

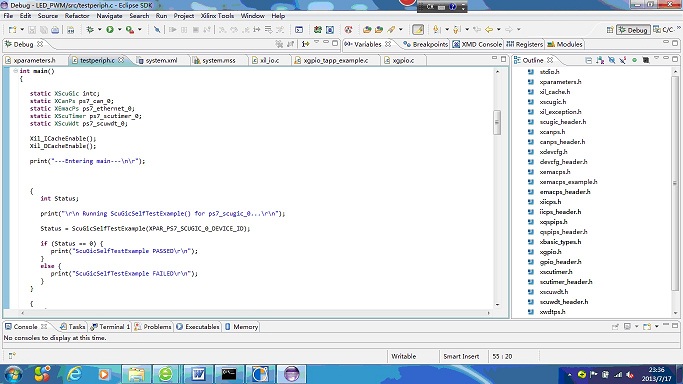

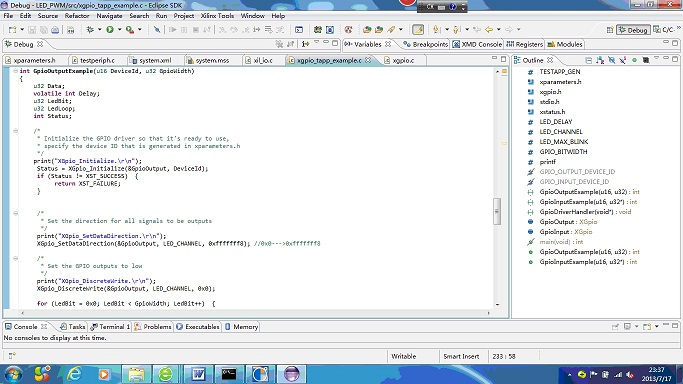

下图是配置axi_gpio这个IP core ,前两个bank只能做MIO用,后面bank3/4是可以通过PL输出的(EMIO),我现在使用gpio的bank3(即第一组EMIO),要实现此功能我配置了图一和图二,当然还需要在planAhead的约束文件中指定具体管脚,见图三。经过一番折腾,测试系统终于跑通——回复可见内容——

图三

图四

图五

图六

图七

图八

图九

图十

图十一

图十二

图十三

图十四

图十五

——回复可见内容——

——回复可见内容——

图十六

[/hid]

我要赚赏金

我要赚赏金