开发板测试无误后,心里一直痒痒的,毕竟那代码不是我写的,现在对软件也不是很熟悉,构建并设置自己的工程,编写自己的代码,看到自己的现象,那才够意思!

在共享里找到了一个《QuartusII12.0安装与使用指南》的资料,照着做了一下,新建了一个Verilog工程,到选择芯片的时候,发现他要选择EP4CE10E22C8,而咱们的芯片貌似是EPM240T100C5H,当时倒也没在意,照着弄吧,一步步做,输入代码、综合分析、配置引脚,这会儿对着原理图,果断发现引脚与原理图不同,原来这个资料是FPGA的,虽然是一样的软件,代码也差不多,不过引脚、芯片都弄出了,肯定出不了现象。都到了这步了,还是下载一下看看吧,果然,第一次成功的失败了。。。

不过通过这手把手的操作,倒是学会了基本的软件操作了,包括建立工程、编写代码的步骤、配置工程、指定引脚等等,既然软件是这样设置的,那估计CPLD的操作也差不多吧。。。当时没多想,也就失败后鼓励自己吧,毕竟,阿Q精神有时候挺管用的。。。

又找到了另一个资料《芯创电子手把手教你学习FPGA—LED篇》,这个倒是实打实的了,仔细的看了第一个实验的实现过程,发现缺少工程构建部分,就按照上次失败的方法做吧,新建工程、输入代码、综合分析、指定引脚、编译、下载。一条龙,由于没看别的资料,心里比较担心,管他呢,不试试怎么能知道结果呢?果然,LED低电平触发,修改了LED端口的二进制代码,还是准确无误,谢谢第一次的错误,最起码让我熟悉了工程的组建和引脚指定。

assign语句和always语句都尝试了一遍,不过单单的亮几个灯还是不够的,再新建一个工程,做下一个实验吧!

尝试LED闪烁!

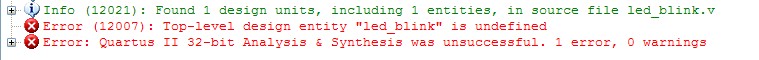

首先扫了一下延时的原理,用到了计数器的累积,和单片机的函数体延时大同小异,也没管那么多,先照着用,至于可不可以用单片机的循环等待或者是别的方式,待看到现象后再深究代码!一条龙操作,综合分析的时候出错了!上图:

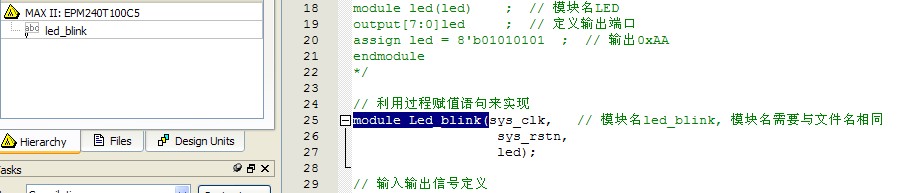

提示 Error (12007): Top-level design entity "led_blink" is undefined。怎么没有定义呢?仔细一看,工程名是小写,而模块声明后跟的是大些如图

改成小写吧,妥善解决问题,编译下载,终于好了!原来模块申明后的模块名和工程建立时的工程名必须一样,懂了。。。

两个LED的小实验都通过了,不过这次只是依葫芦画瓢,这些代码是什么意思还没有弄明白呢,不弄明白它们,迟早是个“祸害”,会影响进度滴!下一步就是看看这些代码是什么意思,Verilog HDL与C语言又有何异同?深究一下语言吧!

我要赚赏金

我要赚赏金