wanderer8885的进程贴

关键词: wanderer8885 进程

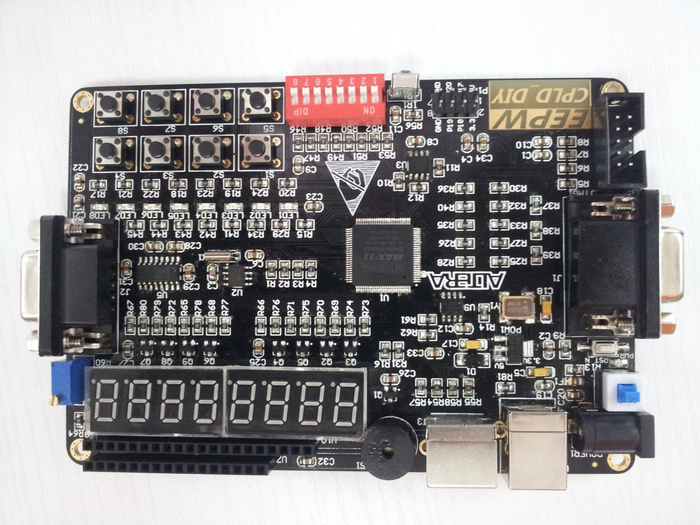

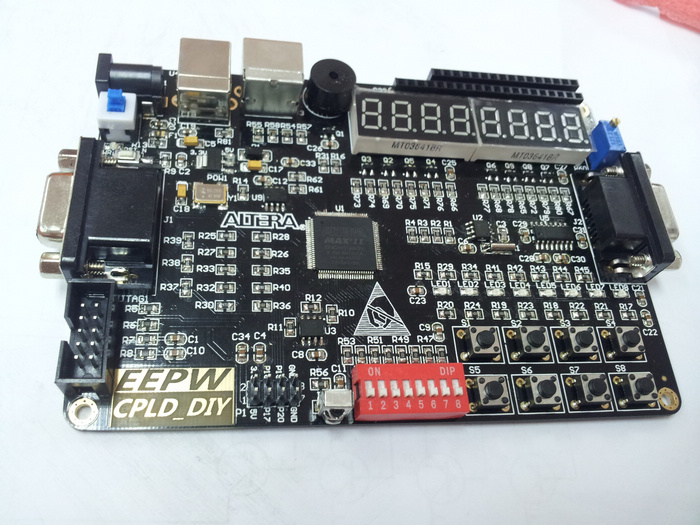

然后就是焊接,整个过程比较顺利,就是看板子漂亮,想把每个焊点都焊好,费了不少功夫。先焊电源部分,测电压,正常;然后焊有源晶振,本来想用示波器测下输出再焊主芯片,结果示波器同事在用,就继续了。顺序自然是先矮后高,因为是无铅焊锡,一个焊点加热5秒以上流动性就明显变差,被烙铁带起来的锡刺挺烦人。整整4个小时才焊完,累。

不得不说下那个LM75温度传感芯片,芯片上居然没有标第一脚,最后看淘宝上的带标识的,根据文字方向猜的,从这个方向看文字刚好是倒的,也不知道对不对,现在还没用到,希望没搞错。

数码管和蜂鸣器两个程序都正常,看来焊接还是比较成功的。于是开始第一个程序——点灯。

虽然以前没接触过verilog HDL语言,但看起来挺顺眼的,所以第一个点灯程序很快写出来了,当然是照着教程。

话说我新学各种语言或新单片机之类的,这第一个hello world程序就从来没有一次写成过,所以点灯程序也是,一综合就报错了,最后发现第一行少写个分号,肯定是受C语法的影响。。。

刚才在电脑里找了下,居然找不到第一个工程,被我给删了,只留了个文本文档的代码做个纪念,不过这些基本的东西大家估计都见多了,没什么好看的,就免了。下面是我第一个流水灯,这个不是参考论坛里的教程,而是网上别处找的,说实话,一开始对这个Verilog HDL语言真的搞不清楚,所有教程里都是一个例子,却很少告诉你为什么这么些,为什么有时候要定义寄存器有时又不用,有时需要定义wire,有时却直接输出。我不太喜欢动不动就求教,决定先照抄,多见几个例子也许就找到规律了。但一定要找比较规范的例子抄,不然在学习初期肯定会混乱思维。

不知道怎么传视频,一会到置顶贴学习一下。先把代码发上来。

这是个并行流水灯,就是每个LED都是独立一个定时模块,分别在各自的时段亮0.1秒,看起来像是顺序依次亮起,其实是并行不悖的。第一个程序就这么长,敲的好累。对了,说程序实在是不恰当,应该说是建模,据说学这个一定要摒除以前C语言的顺序执行思维,要以“偏向并行”思维方式思考,才更符合底层的结构,更符合实际应用。

/*******

********/

module para_led_top(clk,rst_n,LEDout);

input clk;

input rst_n;

output[7:0] LEDout;

wire LEDout1;

led0 u0(.clk(clk),.rst_n(rst_n),.ledout(LEDout1));

wire LEDout2;

led1 u1(.clk(clk),.rst_n(rst_n),.ledout(LEDout2));

wire LEDout3;

led2 u2(.clk(clk),.rst_n(rst_n),.ledout(LEDout3));

wire LEDout4;

led3 u3(.clk(clk),.rst_n(rst_n),.ledout(LEDout4));

wire LEDout5;

led4 u4(.clk(clk),.rst_n(rst_n),.ledout(LEDout5));

wire LEDout6;

led5 u5(.clk(clk),.rst_n(rst_n),.ledout(LEDout6));

wire LEDout7;

led6 u6(.clk(clk),.rst_n(rst_n),.ledout(LEDout7));

wire LEDout8;

led7 u7(.clk(clk),.rst_n(rst_n),.ledout(LEDout8));

assign LEDout = {LEDout8,LEDout7,LEDout6,LEDout5,LEDout4,LEDout3,LEDout2,LEDout1};

endmodule

/**********************************************/

module led0(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 1'b0 && count < 26'd5_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led1(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd5_000_000 && count < 26'd10_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led2(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd10_000_000 && count < 26'd15_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led3(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd15_000_000 && count < 26'd20_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led4(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd20_000_000 && count < 26'd25_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led5(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd25_000_000 && count < 26'd30_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led6(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd30_000_000 && count < 26'd35_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

/**********************************************/

module led7(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

parameter T800MS = 26'd40_000_000;

reg[26:0] count;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count<=1'b0;

else if(count == T800MS)

count<=1'b0;

else

count<=count+1'b1;

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r<=1'b1;

else if(count >= 26'd35_000_000 && count < 26'd40_000_000)

ledout_r<=1'b0;

else

ledout_r<=1'b1;

assign ledout = ledout_r;

endmodule

下面一个也是流水灯,真是永远的流水灯,入门必学。

这个流水灯是led8独自以1Hz的频率闪烁,led1-led7以0.1秒的间隔顺序闪烁。

module led_mix_top(clk,rst_n,LEDout);

input clk;

input rst_n;

output[7:0] LEDout;

wire led_f_out;

led_flash u1(.clk(clk),.rst_n(rst_n),.ledout(led_f_out));

wire[6:0] led_r_out;

led_run u2(.clk(clk),.rst_n(rst_n),.ledout(led_r_out));

assign LEDout = {led_f_out,led_r_out};

endmodule

/********************************************/

//

/********************************************/

module led_flash(clk,rst_n,ledout);

input clk;

input rst_n;

output ledout;

/***************************/

reg[24:0] count;

parameter T_500MS = 25'd25_000_000; //50MHz CLK

always@(posedge clk or negedge rst_n)

if(!rst_n)

count <= 1'b0;

else if(count == T_500MS)

count <= 1'b0;

else

count <= count + 1'b1;

/***************************/

reg ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r <= 1'b1;

else if(count == T_500MS)

ledout_r <= ~ledout_r;

assign ledout = ledout_r;

endmodule

/********************************************/

//

/********************************************/

module led_run(clk,rst_n,ledout);

input clk;

input rst_n;

output[6:0] ledout;

/***************************/

reg[15:0] count;

parameter T_1MS = 16'd50_000; //50MHz CLK

always@(posedge clk or negedge rst_n)

if(!rst_n)

count <= 1'b0;

else if(count == T_1MS)

count <= 1'b0;

else

count <= count + 1'b1;

/***************************/

reg[6:0] count_ms;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count_ms <= 1'b0;

else if(count_ms == 7'd100)

count_ms <= 0;

else if(count == T_1MS)

count_ms <= count_ms + 1'b1;

/***************************/

reg[6:0] ledout_r;

always@(posedge clk or negedge rst_n)

if(!rst_n)

ledout_r <= 7'b1111110;

else if(ledout_r == 7'b1111111)

ledout_r <= 7'b1111110;

else if(count_ms == 7'd100)

ledout_r <= {ledout_r[5:0],1'b1};

assign ledout = ledout_r;

endmodule

流水灯流完了,然后就是数码管了,这个驱动起来了方便调试。

网上很多例程都是1234567,没一点创意,我就想来个数字会变动的,最简单的就是显示一个自加的数。

可实际操作才发现,如果一秒自加一下,8位数码管最高位那个动一下我得等半年,算了,还是加快点,只用四位,左右对称,16进制显示循环自加。这样看起来至少觉得东西是个活的。

module segment

(

clk ,

reset_n,

// wire[6:0] led_seg ,

led_seg,

// wire[7:0] led_dig

led_dig

);

input clk;

input wire reset_n;

output led_seg;

output led_dig;

reg[6:0] led_seg;

reg[7:0] led_dig;

reg[31:0] count;

reg[2:0] refresh;

reg[3:0] disdata;

always @ ( posedge clk or negedge reset_n)

if (!reset_n)

begin

count<=0;

end

else

begin

count<=count+1;

end

always @ ( count[16] )

begin

refresh = {count[18:16]};

end

always @ ( refresh )

begin

case (refresh)

4'b0000: begin

led_dig <= ~8'b00000001; // 0

disdata = {count[19:16]};

end

4'b0001:begin

led_dig <= ~8'b00000010; // 1

disdata = {count[23:20]};

end

4'b0010:begin

led_dig <= ~8'b00000100; // 2

disdata = {count[27:24]};

end

4'b0011:begin

led_dig <= ~8'b00001000; // 3

disdata = {count[31:28]};

end

4'b0100:begin

led_dig <= ~8'b00010000; // 4

disdata = {count[31:28]};

end

4'b0101:begin

led_dig <= ~8'b00100000; // 5

disdata = {count[27:24]};

end

4'b0110:begin

led_dig <= ~8'b01000000; // 6

disdata = {count[23:20]};

end

4'b0111:begin

led_dig <= ~8'b10000000; // 7

disdata = {count[19:16]};

end

default: led_dig <= ~8'b00000000;

endcase

end

always @ ( refresh )

begin

case (disdata)

4'b0000: led_seg <= ~7'b0111111; // 0

4'b0001: led_seg <= ~7'b0000110; // 1

4'b0010: led_seg <= ~7'b1011011; // 2

4'b0011: led_seg <= ~7'b1001111; // 3

4'b0100: led_seg <= ~7'b1100110; // 4

4'b0101: led_seg <= ~7'b1101101; // 5

4'b0110: led_seg <= ~7'b1111101; // 6

4'b0111: led_seg <= ~7'b0100111; // 7

4'b1000: led_seg <= ~7'b1111111; // 8

4'b1001: led_seg <= ~7'b1101111; // 9

4'b1010: led_seg <= ~7'b1110111; // A

4'b1011: led_seg <= ~7'b1111100; // b

4'b1100: led_seg <= ~7'b0111001; // c

4'b1101: led_seg <= ~7'b1011110; // d

4'b1110: led_seg <= ~7'b1111001; // E

4'b1111: led_seg <= ~7'b1110001; // F

default: led_seg <= ~7'b1111111;

endcase

end

endmodule

经过了数码管建模,似乎有了一点点感觉,于是开始解码时序,最先选择肯定是经典的串口了。

下面是串口接收一个字节,并以8位LED显示,亮为1,灭为0,高8位为led8。

/*********************************************/

/*********************************************/

module rx_232_top(clk,rst_n,rx_pin_in,rx_data);

input clk;

input rst_n;

input rx_pin_in;

output[7:0] rx_data;

wire[7:0] Rx_data_in;

wire Rx_done_sig;

rx U4(.clk(clk),.rst_n(rst_n),

.rx_pin_in(rx_pin_in),

.rx_en_sig(Rx_en_sig),

.rx_done_sig(Rx_done_sig),

.rx_data(Rx_data_in));

wire[7:0] RX_data_out;

wire Rx_en_sig;

control U5(.clk(clk),.rst_n(rst_n),

.rx_en_sig(Rx_en_sig),

.rx_done_sig(Rx_done_sig),

.rx_data_in(Rx_data_in),

.rx_data_out(RX_data_out)

);

assign rx_data = ~RX_data_out;

endmodule

/*********************************************/

/*********************************************/

module control(

clk,rst_n,

rx_en_sig,

rx_done_sig,

rx_data_in,

rx_data_out

);

input clk;

input rst_n;

input rx_done_sig;

input[7:0] rx_data_in;

output rx_en_sig;

output[7:0] rx_data_out;

reg[7:0] rx_data_r;

reg isEn;

always@(posedge clk or negedge rst_n)

if(!rst_n)

rx_data_r <= 8'd0;

else if(rx_done_sig)

begin

rx_data_r <= rx_data_in;

isEn <= 1'b0;

end

else

isEn <= 1'b1;

/***************************/

assign rx_data_out = rx_data_r;

assign rx_en_sig = isEn;

/***************************/

endmodule

/*********************************************/

/*********************************************/

module rx(clk,rst_n,rx_pin_in,rx_en_sig,rx_done_sig,rx_data);

input clk;

input rst_n;

input rx_pin_in;

input rx_en_sig;

output rx_done_sig;

output[7:0] rx_data;

wire h2l_sig;

detect U1( .clk(clk),.rst_n(rst_n),.rx_pin_in(rx_pin_in),.h2l_sig(h2l_sig) );

wire bps_clk;

rs_bps U2( .clk(clk),.rst_n(rst_n),.count_sig(count_sig),.bps_clk(bps_clk) );

wire count_sig;

rx_control U3(

.clk(clk),.rst_n(rst_n),.h2l_sig(h2l_sig),.rx_pin_in(rx_pin_in),

.bps_clk(bps_clk),.rx_en_sig(rx_en_sig),.count_sig(count_sig),

.rx_data(rx_data),.rx_done_sig(rx_done_sig));

endmodule

/*********************************************/

/*********************************************/

module detect( clk,rst_n,rx_pin_in,h2l_sig );

input clk;

input rst_n;

input rx_pin_in;

output h2l_sig;

/***************************/

reg h2l_f1;

reg h2l_f2;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

h2l_f1 <= 1'b1;

h2l_f2 <= 1'b1;

end

else

begin

h2l_f1 <= rx_pin_in;

h2l_f2 <= h2l_f1;

end

/***************************/

assign h2l_sig = h2l_f2 & !h2l_f1;

/***************************/

endmodule

/*********************************************/

/*********************************************/

module rs_bps( clk,rst_n,count_sig,bps_clk );

input clk;

input rst_n;

input count_sig;

output bps_clk;

/***************************/

reg[12:0] count_bps;

always@(posedge clk or negedge rst_n)

if(!rst_n)

count_bps <= 13'd0;

else if(count_bps == 13'd5207) //50M/9600 = 5208

count_bps <= 13'd0;

else if(count_sig)

count_bps <= count_bps + 1'b1;

else

count_bps <= 13'd0;

/***************************/

assign bps_clk = (count_bps == 13'd2604) ? 1'b1 : 1'b0 ;

/***************************/

endmodule

/*********************************************/

/*********************************************/

module rx_control(

clk,rst_n,h2l_sig,rx_pin_in,

bps_clk,rx_en_sig,count_sig,

rx_data,rx_done_sig);

input clk;

input rst_n;

input h2l_sig;

input rx_pin_in;

input bps_clk;

input rx_en_sig;

output count_sig;

output rx_done_sig;

output[7:0] rx_data;

/***************************/

reg [3:0] i;

reg [7:0] data_r;

reg isCount;

reg isDone;

always@(posedge clk or negedge rst_n)

if(!rst_n)

begin

i <= 4'd0;

data_r <= 8'd0;

isCount <= 1'b0;

isDone <= 1'b0;

end

else if(rx_en_sig)

case(i)

4'd0:

if(h2l_sig)

begin

i <= i + 1'b1;

isCount <= 1'b1;

end

4'd1:

if(bps_clk) begin i <= i + 1'b1; end

4'd2,4'd3,4'd4,4'd5,4'd6,4'd7,4'd8,4'd9:

if(bps_clk)

begin

i <= i + 1'b1;

data_r[i-2] <= rx_pin_in;

end

4'd10:

if(bps_clk)

begin

i <= i + 1'b1;

end

4'd11:

if(bps_clk)

begin

i <= i + 1'b1;

end

4'd12:

begin

i <= i + 1'b1;

isDone <= 1'b1;

isCount <= 1'b0;

end

4'd13:

begin

i <= 1'b0;

isDone <= 1'b0;

end

endcase

/***************************/

assign count_sig = isCount;

assign rx_data = data_r;

assign rx_done_sig = isDone;

/***************************/

endmodule

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |