看一篇FPGA的练习的文章,其中作了一个比较,用cycloneII自带的乘法器,和用LE做了一个乘法器,前者没有消耗LE,后者消耗了108个LE。城发起的设置是一样的,都是三级流水。

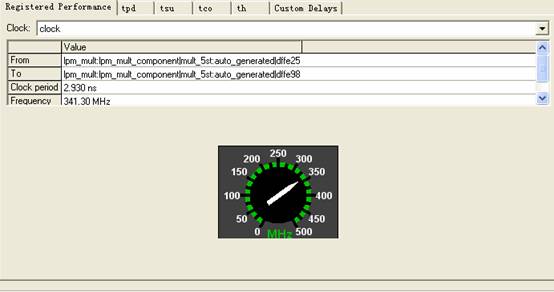

自带的乘法器跑到260MHz,用LE做的乘法器就跑到340MHz,所以体现了“速度与面积”不可兼得的关系。

请教方家,如何知道一个设计可以跑到多少多少MHz?这个数值有何意义?比如,确定我们自己最终的设计的工作频率,比这个值小,留出一定裕量?

用自带的乘法器,面积小了,速度就慢,是如何慢的?是不是并非消耗了更多的时钟数,而是在一个时钟里逻辑更复杂,延时长,所以使时钟变慢了?

我要赚赏金

我要赚赏金