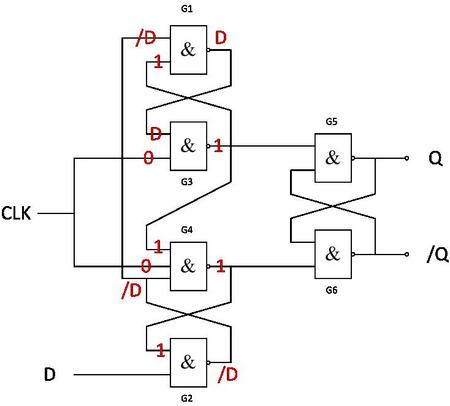

最近一直在纠结建立时间和保持时间,D触发器的结构众多,在网上挑了边沿D触发器(上升沿触发)的结构分析一下,碰到了问题:

所有与非门的延迟先暂不考虑。

1,当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,

不受输入影响。

。

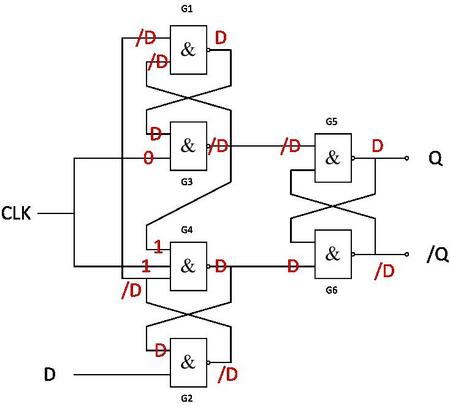

2,当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q

再考虑与非门的延时。

设G2和G1 的延迟为T1,当CLK=0时,如果D在时钟跳变前的T(T<T1)时间才从d1更新为d2,那么G1和G2在时钟跳变时刻的输出值肯定是d1和/d1,而不是d2和/d2,进而影响到G3和G4的输出。如果要使得G1和G2的输出为d2和/d2,就必须要求D起码在时钟跳变之前的T1时间内维持d2稳定不变。这个T1就是建立时间Tsu。这个还可以理解。

当CLK=1时,G3和G4的延迟为T2,当CLK=1时,如果D在时钟跳变之后的T(T<T2)时间从d2更新为d3,由于G3和G4的输出在T的时间内还保持为1,所以D的更新会影响G2和G1的输出,进而影响G3和G4的输出,进而影响G5和G6的输出,造成输出Q和/Q不稳。T2为保持时间。

clk = 1时,D在时钟跳变之后的T时间从d2更新d3,G3,G4的输出由于延时在T时间内还保持为1,

问题来了,D的更新也会受到G1,G2 的延时啊,所以D更新如何影响G1,G2的输出啊?此时的输出应该保持才对啊,虽然我知道我的理解有问题,但是不知道错在哪里?恳求各位大大指教。

我要赚赏金

我要赚赏金