74HC595——具有三态输出锁存功能的8位串行输入、串行/并行输出移位寄存器

本文翻译自NXP的74HC595的datasheet

74HC595和74HCT595是带有存储寄存器和三态输出的8位串行移位寄存器,移位寄存器和存储寄存器有各自的时钟。

每当移位寄存器输入时钟SHCP上升沿来临之时,数据被移出。

每当存储寄存器输入时钟STCP上升沿来临之时,数据并行的存储到存储寄存器。如果两个时钟上升沿同时到来,移位寄存器总是要比存储寄存器的提前一个时钟。

移位寄存器有一个串行出入(DS)和一个串行标准输出(Q7S)。同时也提供一个异步复位端(低电平有效),存储寄存器有一个8位3态总线输出。输出使能(OE)为低电平时,存储寄存器的值就输出。

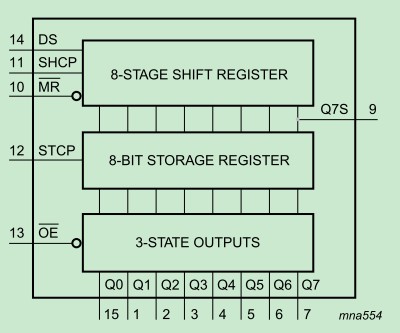

下面是一个功能框图,有利于理解:

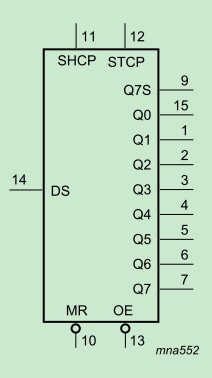

接着是一个逻辑符号:

各引脚的的说明如下:

| 符号 | 引脚 | 描述 |

| Q1 | 1 | 并行输出1 |

| Q2 | 2 | 并行输出2 |

| Q3 | 3 | 并行输出3 |

| Q4 | 4 | 并行输出4 |

| Q1 | 5 | 并行输出5 |

| Q2 | 6 | 并行输出6 |

| Q3 | 7 | 并行输出7 |

| GND | 8 | 接地 |

| Q7S | 9 | 串行数据输出 |

| MR | 10 | (master reset)复位-低电平有效 |

| SHCP | 11 | 移位寄存器输入时钟(shift register clock iuput) |

| STCP | 12 | 存储寄存器输入时钟(storage register clock iuput) |

| OE | 13 | 输出使能(地电位有效) |

| DS | 14 | 串行数据输出输入 |

| Q0 | 15 | 并行数据输出0 |

| Vcc | 16 | 电源 |

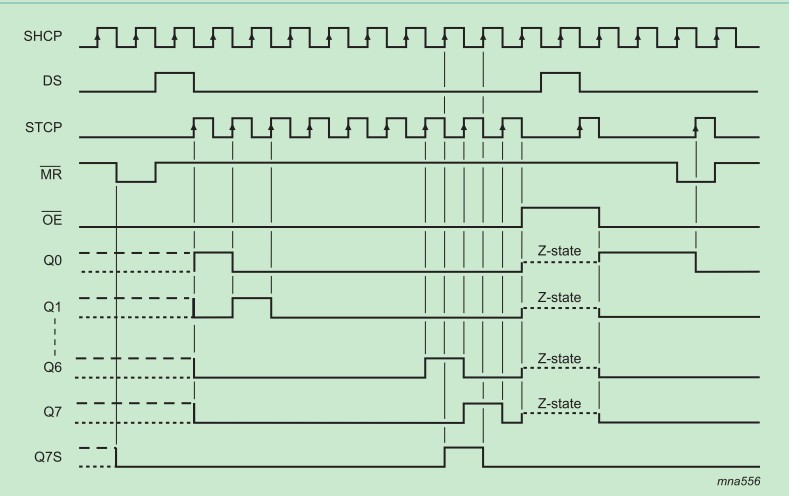

时序图:

我要赚赏金

我要赚赏金