今在研究Cadence原理图的时候,发现了一篇文章中介绍到可以将AD下的原理图导入到Cadence中如下:

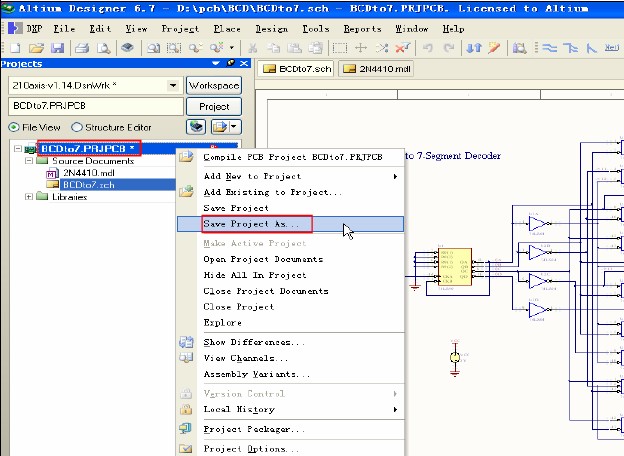

在Altium Designer 6 原理图的转化上我们可以利用Altium Designer 6 的Save Preject As 来实现。通过这一功能我们可以直接将AD6 的原理图转化到Capture CIS 中。

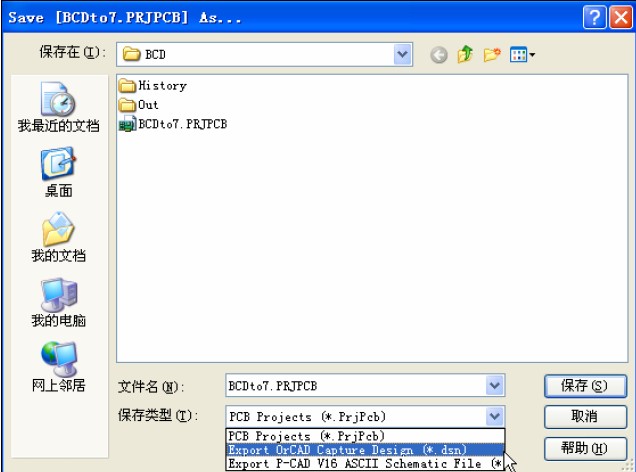

1、AD6的工程另存为(*。dsn)

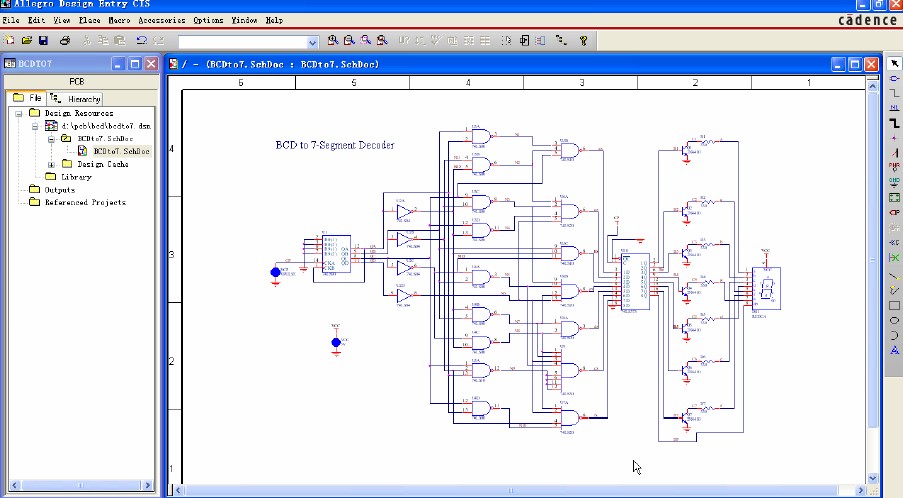

2、在Cadence capture CIS中导入

注意事项: 这里,我们仅提出几点通过实践总结出来的注意事项。

a)封装信息

AD6 在输出Capture DSN 文件的时候,没有输出封装信息,在Capture 中我们会看到所以元件的PCB Footprint 属性都是空的。这就需要我们手工为元件添加封装信息,这也是整个转化过程中最耗时的工作。在添加封装信息时要注意保持与AD6 PCB 设计中的封装一致性,以及Cadence 在封装命名上的限制。例如一个电阻,在 AD6 中的封装为AXIAL0.4,在后面介绍的封装库的转化中,将被修改为AXIAL04,这是由于Cadence 不允许封装名中出现“.”;再比如DB9 接插件的封装在AD6 中为DB9RA/F,将会被改为DB9RAF。因此我们在Capture 中给元件添加封装信息时,要考虑到这些命名的改变。当然,如果自己有一些标准的Cadence 的PCB 封装库,也可以直接输入对应的封装库名称。只是需要注意的就是在后面要导入器件的位置信息的时候,需要把AD6 中的PCB 封装名称修改为Cadence 的PCB 封装名称。当然两个软件中封装库的原点应该是一致的,否则后面导入PCB Editor 时候,器件不在原来的位置。

b)原始设计要规范

AD6 的原理图应该要规范,保证导出之后的错误尽可能的少,譬如,网络的连线最好不要直接连接到pin 管脚,应该来出来一段线之后再去连接其他管脚。还有电源地符号,最好在AD6 中引出一段线再接。

c)管脚信息

一些器件的隐藏管脚或管脚号在转化过程中会丢失,需要在Capture 中使用库编辑的方法添加上来。通常易丢失管脚号的器件时电阻电容等离散器件。

d)层次化设计中的问题

在层次化设计中,模块之间连接的总线需要在 Capture 中命名。即使在AD6 中已经在设计中对这样的总线命名了,还是要在Capture 中重新来过,以确保连接。

补充:我在AD10中按照上述方法试了,但是没成功,有用Cadence+AD6的同志们没,不妨试一下。

我要赚赏金

我要赚赏金