小菜鸟刚刚上路……求指点……用verilog语言写的,用查表法实现NCO,

采用的芯片是Altera公司开发的CycloneIII系列中的EP3C40F484C8芯片,系统时钟为102.4MHz

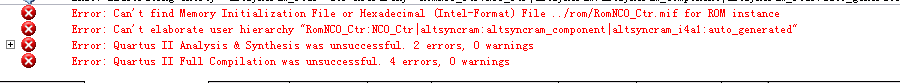

,提示有4个错误,不知道从哪里入手啊。。。妹子是新手,各种不懂啊。。。跪求高手!!!

module FreqMix(

//input interferes

clk,

data_c0,

mgc,

NCO_Switch,

//output interferes

result_c0,

result_c1,

data_sin_r,

data_cos_r);

input clk;

input [13:0] data_c0;//Sample digital data

input [7:0] mgc;//demodulation gain

input [8:0] NCO_Switch;

output [16:0] result_c0;

output [16:0] result_c1;

reg [9:0] address_sin;

reg [9:0] address_cos;

wire [17:0] data_sin;

wire [17:0] data_cos;

wire [8:0] Fre_Ctr;

output reg [17:0] data_sin_r;

output reg [17:0] data_cos_r;

reg [13:0] data_buf_c0;

wire [31:0] result_m_c0;

wire [31:0] result_m_c1;

reg [17:0] result_r_c0;

reg [17:0] result_r_c1;

reg [17:0] result_r0_c0;

reg [17:0] result_r0_c1;

always @ (posedge clk)

begin

data_buf_c0 <= data_c0;

end

always @ (posedge clk)

begin

//sin function's address

address_sin<=address_sin+Fre_Ctr;

//cos function's address

address_cos<=address_sin+Fre_Ctr+10'd256;

end

always @ (posedge clk)

begin

data_sin_r<=data_sin;

data_cos_r<=data_cos;

end

RomNCO_Ctr NCO_Ctr

(.clock(clk),.address(NCO_Switch),.q(Fre_Ctr));

//Through LUT,find the sin/cos data

RomFreqMixA RomFreqMixA_inst

(.address_a(address_sin),.address_b(address_cos),.clock(clk),.q_a(data_sin),.q_b(data_cos));

//Data multiply sin function,result is I signal

MultMix MultMix_inst_c0

(.dataa(data_buf_c0),.datab(data_sin_r),.clock(clk),.result(result_m_c0));

//Data multiply cos function,result is Q signal

MultMix MultMix_inst_c1

(.dataa(data_buf_c0),.datab(data_cos_r),.clock(clk),.result(result_m_c1));

always @ (posedge clk)

begin

case(mgc)

8'h01:begin

result_r_c0<=result_m_c0[29:12];

result_r_c1<=result_m_c1[29:12];

end

8'h02:begin

result_r_c0<=result_m_c0[28:11];

result_r_c1<=result_m_c1[28:11];

end

8'h03:begin

result_r_c0<=result_m_c0[27:10];

result_r_c1<=result_m_c1[27:10];

end

8'h04:begin

result_r_c0<=result_m_c0[26:9];

result_r_c1<=result_m_c1[26:9];

end

8'h05:begin

result_r_c0<=result_m_c0[25:8];

result_r_c1<=result_m_c1[25:8];

end

8'h06:begin

result_r_c0<=result_m_c0[24:7];

result_r_c1<=result_m_c1[24:7];

end

8'h07:begin

result_r_c0<=result_m_c0[23:6];

result_r_c1<=result_m_c1[23:6];

end

8'h08:begin

result_r_c0<=result_m_c0[22:5];

result_r_c1<=result_m_c1[22:5];

end

8'h09:begin

result_r_c0<=result_m_c0[21:4];

result_r_c1<=result_m_c1[21:4];

end

/*8'h0A:begin

result_r_c0<=result_m_c0[20:3];

result_r_c1<=result_m_c1[20:3];

end

8'h0B:begin

result_r_c0<=result_m_c0[19:2];

result_r_c1<=result_m_c1[19:2];

end

8'h0C:begin

result_r_c0<=result_m_c0[18:1];

result_r_c1<=result_m_c1[18:1];

end

8'h0D:begin

result_r_c0<=result_m_c0[17:0];

result_r_c1<=result_m_c1[17:0];

end*/

default:begin

result_r_c0<=result_m_c0[30:13];

result_r_c1<=result_m_c1[30:13];

end

endcase

result_r0_c0<=result_r_c0+18'd1;

result_r0_c1<=result_r_c1+18'd1;

end

//The mode of operation reduces the effects of digital output inerferance

assign result_c0 = result_r0_c0[17:1];

assign result_c1 = result_r0_c1[17:1];

endmodule

我要赚赏金

我要赚赏金