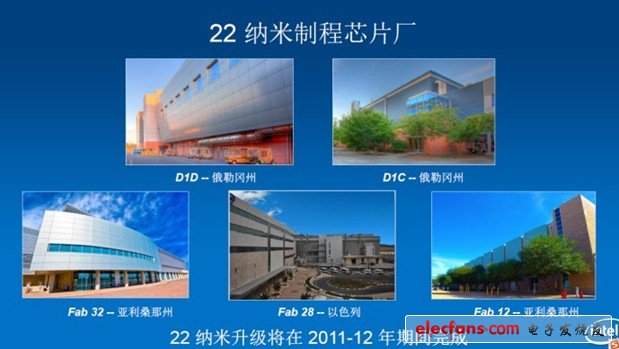

本文核心议题:通过本文介绍,我们将对Intel 22nm 3D三栅极晶体管技术有着详细的了解。业界一直传说3D三栅级晶体管技术将会用于下下代14nm的半导体制造,没想到英特尔竟提前将之用于22nm工艺,并且于上周四向全世界表示将在年底进行规模量产,批量投产研发代号Ivy BRIDGE的22纳米英特尔CPU,并在美国展示了这款处理器。计划中将有五个22nm制程芯片厂工厂同时转入22nm 3D晶体管制程。如下图。

用了50多年的2D平面硅晶体管将被3D晶体管所取代,这确是一种划时代的进步。虽然其它半导体阵营如IBM也有类似的技术研究,但此次英特尔是首次宣布已能进行大规模量产。这一发布令业界无不惊叹:半导体技术又获得了新生,摩尔定律又得以延续。英特尔的确太伟大了,它带领全球半导体业又迈上的新的台阶。摩尔定律创始人戈登?摩尔对此次突破性的革命给出了很高的评价: “在多年的探索中,我们已看到晶体管尺寸缩小所面临的极限。今天这种在基本结构层面上的改变,是一种真正革命性的突破,它能够让摩尔定律以及创新的历史步伐继续保持活力。”

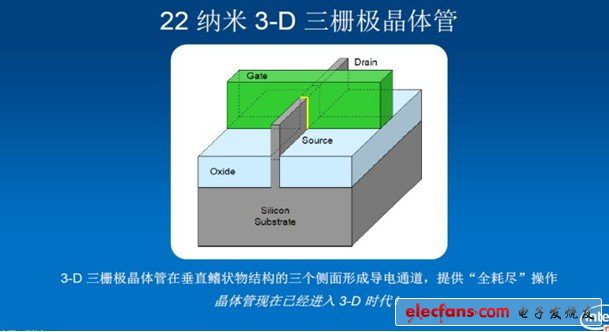

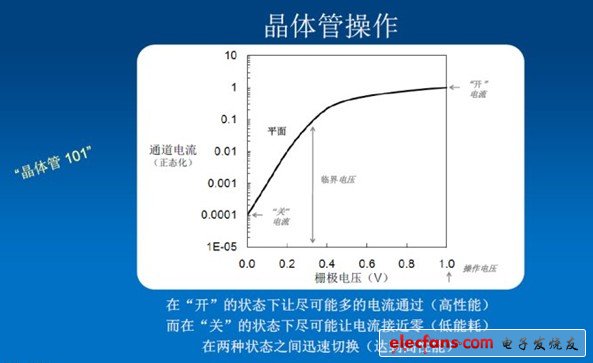

什么是3D三栅极晶体管技术呢?如下图:22nm3D三栅极晶体管在垂直鳍状物结构的三个侧面形成导电通道,提供“全耗尽”操作,至此,晶体管已经进入3D时代。传统“平面的”2-D平面栅极被超级纤薄的、从硅基体垂直竖起的3-D硅鳍状物所代替。电流控制是通过在鳍状物三面的每一面安装一个栅极而实现的(两侧和顶部各有一个栅极),而不是像2-D平面晶体管那样,只在顶部有一个栅极。更多控制可以使晶体管在“开”的状态下让尽可能多的电流通过(高性能),而在“关”的状态下尽可能让电流接近零(即减少漏电,低能耗),同时还能在两种状态之间迅速切换,进一步实现更高性能。

就像摩天大楼通过向天空发展而使得城市规划者优化可用空间一样,英特尔的3-D三栅极晶体管结构提供了一种管理晶体管密度的方式。由于这些鳍状物本身是垂直的,晶体管也能更紧密地封装起来——这是摩尔定律追求的技术和经济效益的关键点所在。未来,设计师还可以不断增加鳍状物的高度,从而获得更高的性能和能效。

目前几种主流3D晶体管技术的比较

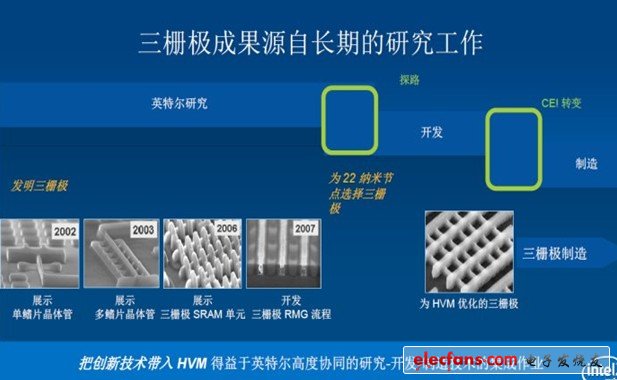

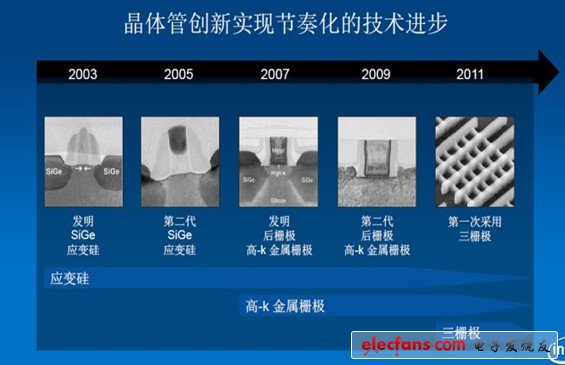

“事实上,英特尔在十年前就已成功研发出单鳍片晶体管,随后研出发多鳍片晶体管、三栅极SRAM单元以及三栅极RMG流程(如下图)。这为今天英特尔推出大规模量产的三栅极CPU作好了充分的准备。”英特尔技术与制造事业部亚洲区发言人柯必杰(Kirby Jefferson)在上周北京的记者会上表示,“所以,我们说能大规模生产,是表示我们的生产良率、缺陷率等参数已完全能满足大规模生产的要求,和目前的32nm工艺的水平已非常接近。”他称。

他还比较了英特尔的3D三栅极技术与其它两种3D晶体管技术的区别。“3D三栅极晶体管技术优于Bulk,PDSOI以及FDSOI技术。”他解释,对于Bulk晶体管技术,衬底电压在反型层(源漏电流在其上流动)施加某些电气影响,衬底电压的影响降级电气次临界斜率(晶体管关闭特征),是未完全耗尽的方式;部分耗尽的 SOI(PDSOI),浮体在反型层施加某些电气影响,降级次临界斜率,也是未完全耗尽;全耗尽SOI(FDSOI),浮体消除,而次临界斜率提高,需要昂贵的超薄 SOI 晶圆,这让整体制程成本增加了大约 10%。而英特尔的全耗尽型3D三栅极晶体管,栅极从三个侧面控制硅鳍状物,提高次临界斜率,反型层面积增加,用于更高的驱动电流, 制程成本只增加 2-3%。

注:改图是晶体管的操作过程,能达到高性能、低功耗的状态,在开的状态下让尽可能多的电流通过,在关的状态下尽可能让电流接近零

在两种状态间的话就能迅速切换从而达到高性能的目的。单晶体管功耗下降50%,性能提升37%

我要赚赏金

我要赚赏金