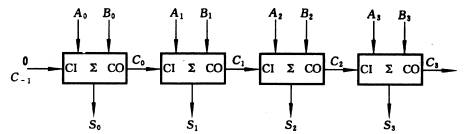

若有多位数相加,则可采用并行相加串行进位的方式来完成。例如,有两个4位二进制数A3A2A1A0和B3B2B1B0相加 ,可以采用两片内含两个全加器或1片内含4个全加器的集成电路组成,其原理图如下图所示:

由图可以看出,每1位的进位信号送给下1位作为输入信号,因此,任1位的加法运算必须在低1位的运算完成之后才能进行,这种进位方式称为串行进位。这种加法器的逻辑电路比较简单,但它的运算速度不高。为克服这一缺点,可以采用超前进位等方式。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| PCF8574功能模块及其使用被打赏¥20元 | |

| 传感器LSM6DSO及LIS3MDL的功能检测被打赏¥18元 | |

| LPS25HB气压传感器及其检测被打赏¥18元 | |

| HTS221温湿度传感器及其检测被打赏¥18元 | |

| 【S32K3XX】HSE FW 版本更新被打赏¥21元 | |

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |