有些电路输出阻抗高,容易受到负载的影响,因此使用射极跟随器,来降低输出阻抗。

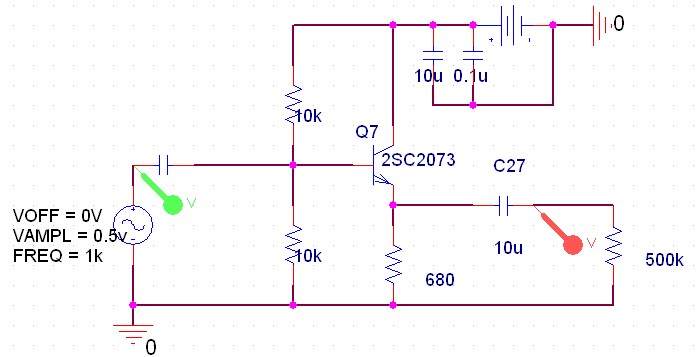

一个典型的射极跟随器电路:

电路仿真图:

这个电路最大的不同是没有了Rc,这个电阻决定了集电极输出的放大倍数。因为输出是在射极,所以这个电阻没有必要,虽然接入也能工作,但是增加了功耗。

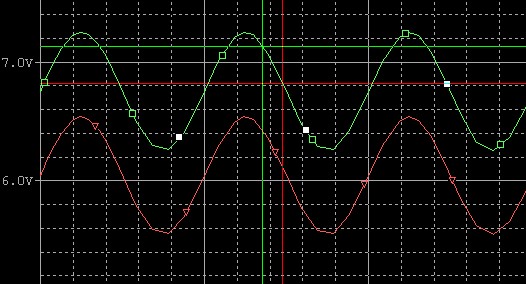

下面的仿真图是发射极电位与基极电位的比较图,可知发射极电位比基极低0.6V,这是由于Vbe上的压降造成的。

负载电阻Rl可看作是与Re并联的,可见RL的变化与Re的变化效果是一样的。然而Ve=Vb-Vbe,其中Vb是分压得到的,固定不变,因此Ve也是一定的,因此输出Vo与Rl和Re的值无关,因此可以看做射极跟随器输出阻抗是0.

如果发射极的直流电位在电源电压和GND的中点,这样就能得到最大的输出振幅。这里取Vb为7.5v,,Ve为7.5-0.6=6.9V。因此VCE=VCC-Vb=8.1V,晶体管集电极损耗Pc=Vce*Ic

我要赚赏金

我要赚赏金