在基于TI DSP芯片TMS320F281X设计的某项目中,由于IO上电时的默认电平不匹配导致系统不能正常工作,本文档将对IO初始电平引发的血案进行分析并给出解决方案。这对于继电器控制、驱动电路等应用而言认识IO状态至关重要。

1 IO上电及复位状态分析

以下将针对常用芯片的IO上电及复位状态进行分析总结:

1.1 TI DSP TMS320F281x芯片

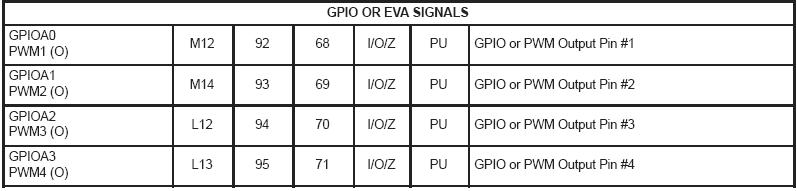

在TMS320F281x数据手册中标明了信号接口是否具备内部上下拉功能,如本例中单路电机驱动电路的4个PWM控制信号接口均有内部上拉。

图 GPIOAx/PWMx+1

在实际测试中发现该4个引脚上电初始或复位状态下均为高电平,直到程序运行(程序中先设置该4个接口为PWM复用功能输出,而后设置PWM输出逻辑)后才按照程序中的配置输出PWM波形,这样在上电到正确输出PWM波形前,驱动电路直侧导通导致系统电源对地短路。

查阅TMS320F281x数据手册,对GPIO有如下的文字描述。从而可知对于有内部上拉的IO口一旦配置为输出,则必然先输出高电平,然后才根据程序配置输出相应电平。

On reset, the default value for all GPxMUX and GPxDIR register bits is 0. That is, at reset all I/O ports are configured as input pins. Before changing the direction of the port from input to output using the GPxDIR register bit, the current level of the pin is reflected in the GPxDAT register. The GPxDAT register is described later in this section. When the direction of the port is changed from input to output, the value already in the GPxDAT register is used to determine the state of the pin.

For example, if a pin has an internal pullup, then after reset the pullup would force the GPxDAT Register bit to a1 to reflect the current state of the pin. When the direction of the port changes from an input to an output the 1 already in the GPxDAT Register forces the pin to the same level. In this manner, the pin can be switched from input to output without a glitch.

——摘自SPRU078D P4-8

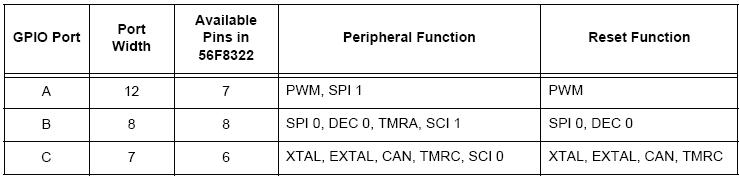

1.2 Freescale DSP 56Fxxx

飞思卡尔系列DSP芯片在上电或复位状态时默认为复用外设功能,实测各接口上电或复位状态时为低电平。

图 56Fxxx

1.3 ST Cortex-M3 STM32

STM32的IO管脚配置口默认为浮空输入,把选择权留给用户,这是一个很大的优势:一方面浮空输入确保不会出现用户不希望的默认电平(此时电平取决于用户的外围电路);另一方面降低了功耗,因为不管是上拉还是下拉,都会有电流消耗。从另一个角度来看,不管I/O管脚的默认配置如何,还是需要在输出的管脚外加上拉或下拉,这是为了保证芯片上电期间和复位时,输出的管脚始终处于已知的电平。

2 案例解决

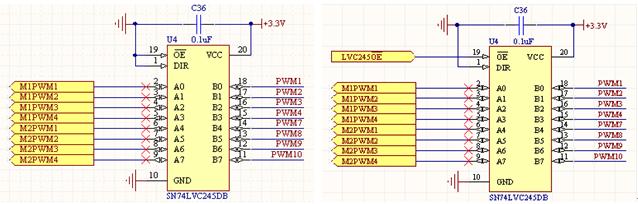

在无法改变TMS320F281x芯片引脚的默认状态的前提下,有两个方法纠正默认电平不匹配的问题:一是使用反相器;二是使用总线收发器芯片并利用其控制端闭锁DSP的信号输出。如下图1所示。

a) 原设计 b)添加输出控制

图1 LVC245输出控制

一般总线收发器都有控制接口:DIR控制传输方向;OE————控制输出(低时正常,高时为高阻态);将OE————用一个IO信号(需为内部上拉的IO口)控制,由于TMS320F281x的上拉IO默认为高电平,则LVC245不工作,在系统启动后更改该IO后低电平输出使之使能,即可将PWM信号送至驱动电路。

我要赚赏金

我要赚赏金