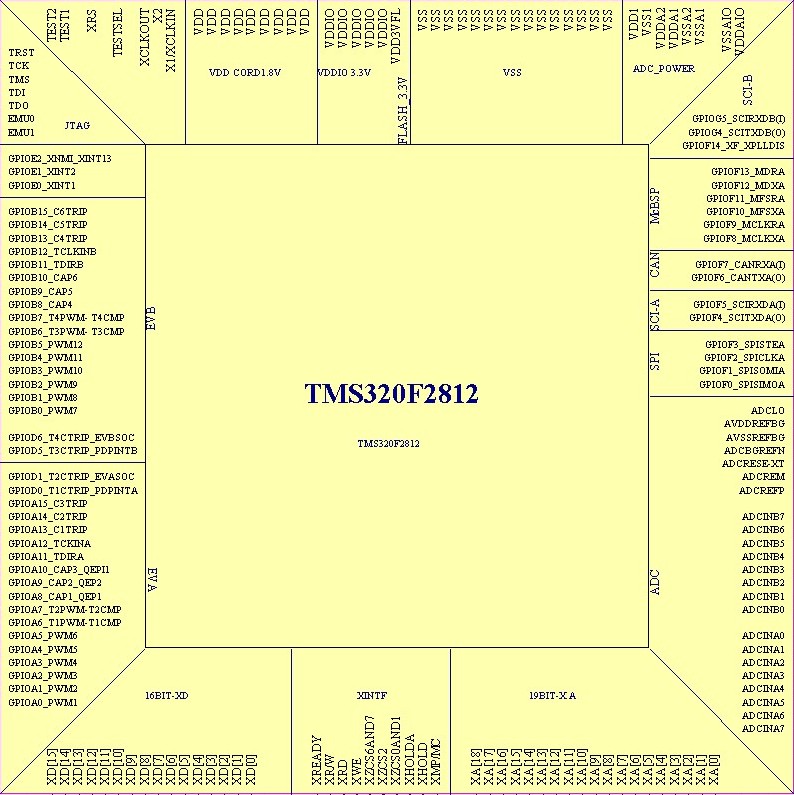

XINTF信号

XA[0]~XA[18] --- 19位地址总线

XD[0]~XD[15] --- 16位数据总线

XMP/MC` --- 1 -- 微处理器模式 --- XINCNF7有效

0 -- 微计算机模式 --- XINCNF7无效

XHOLD` --- 外部DMA保持请求信号。XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。此信号是异步输入并与XTIMCLK同步

XHOLDA` --- 外部DMA保持确认信号。当XINTF响应XHOLD的请求时XHOLDA呈低电平,所有的XINTF总线和选通端呈高阻态。XHOLD和XHOLDA信号同时发出。当XHOLDA有效(低)时外部器件只能使用外部总线

XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)

XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低)

XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)

XWE` --- 写有效。有效时为低电平。写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定

XRD` --- 读有效。低电平读选通。读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。注意:XRD`和XWE`是互斥信号

XR/W` --- 通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期

XREADY --- 数据准备输入,被置1表示外设已为访问做好准备。XREADY可被设置为同步或异步输入。在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREADY有效。在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREADY采样3次。以XTIMCLK频率对XREADY的采样与XCLKOUT的模式无关

JTAG和其他信号

X1/XCLKIN --- 振荡器输入/内部振荡器输入,该引脚也可以用来提供外部时钟。C28x能够使用一个外部时钟源,条件是要在该引脚上提供适当的驱动电平,为了适应1.8V内核数字电源(VDD),而不是3.3V的I/O电源(VLDIO)。可以使用一个嵌位二极管去嵌位时钟信号,以保证它的逻辑高电平不超过VDD(1.8V或1.9V)或者去使用一个1.8V的振荡器

X2 --- 振荡器输出

XCLKOUT --- 源于SYSCLKOUT的单个时钟输出,用来产生片内和片外等待状态,作为通用时钟源。XCLKOU丁与SYSCLKOUT的频率或者相等,或是它的1/2,或是l/4。复位时XCLKOUT=SYSCLKOUT/4

TESTSEL --- 测试引脚,为TI保留,必须接地

TEST1 --- 测试引脚,为TI保留,必须悬空

TEST2 --- 测试引脚,为TI保留,必须悬空

TMS --- JTAG测试模式选择端,有内部上拉功能,在TCK的上升沿TAP控制器计数一系列的控制输入

TDI --- 带上拉功能的JTAG测试数据输入端,在TCK的上升沿,TDI被锁存到选择寄存器、指令寄存器或数据寄存器中

TDO --- JTAG扫描输出,测试数据输出。在TCK的下降沿将选择寄存器的内容从TDO移出

TCK --- JTAG测试时钟,带有内部上拉功能

TRST` --- 有内部上拉的JTAG测试复位。当它为高电平时扫描系统控制器件的操作。若信号悬空或为低电平,器件以功能模式操作,测试复位信号被忽略

注意:TRST`上不要用上拉电阻。它内部有上拉部件。在强噪声的环境中需要使习附加上拉电阻,此电阻值根据调试器设计的驱动能力而定。一般取22K即能提供足够的保护。因为有了这种应用特性,所以使得调试器和应用目际板都有合适且有效的操作

EMU0 --- 带上拉功能的仿真器I/O口引脚0,当TGST`为高电平时,此引脚用作中断输入。该中断来自仿真系统,并通过JTAG扫描定义为输入/输出

EMU1 --- 仿真器引脚1,当TGST`为高电平时,此引脚输出无效,用作中断输入。该中断来自仿真系统的输入,通过JTAG扫描定义为输入/输出

XRS` --- 器件复位(输入)及看门狗复位(输出)。器件复位,XRS使器件终止运行,PC指向地址0x3FFFCO。当XRS为高电平时,程序从PC所指出的位置开始运行。当看门狗产生复位时,DSP将该引脚驱动为低电平,在看门向复位期间,低电平将持续512个XCLKIN周期。该引脚的输出缓冲器是一个带有内部上拉(典型值100mA)的开漏缓冲器,推荐该引脚应该由一个开漏设备去驱动

ADC模拟输入信号

ADCINA7 ~ ADCINA0 --- 采样/保持A的8通道模拟输入。在器件未上电之前ADC引脚不会被驱动

ADCINB7 ~ ADCINB0 --- 采样/保持B的8通道模拟输入。在器件未上电之前ADC引脚不会被驱动

ADCREFP --- ADC参考电压输出(2V)。需要在该引脚上接一个低ESR(50m~1.5欧姆)的10uf陶瓷旁路电容,另一端接至模拟地

ADCREFM --- ADC参考电压输出(1V)。需要在该引脚上接一个低ESR(50m~1.5欧姆)的10uf陶瓷旁路电容,另一端接至模拟地

ADCRESE-XT --- ADC外部偏置电阻(24.9K)

ADCBGREFN --- 测试引脚,为TI保留,必须悬空

AVDDREFBG --- ADC模拟电源(3.3V)

AVSSREFBG --- ADC模拟地

ADCLO --- 普通低侧模拟输入

VSS1 --- ADC数字地

VSSA1、2 --- ADC模拟地

VDD1 --- ADC数字电源(1.8V)

VDDA1、2 --- ADC模拟电源(3.3V)

VDDAIO --- I/O模拟电源(3.3V)

VSSAIO --- I/O模拟地

电源信号

VDD --- 1.8V或1.9V核心数字电源

VSS --- 内核和数字I/O地

VDDAIO --- I/O模拟电源(3.3V)

VDDIO --- I/O数字电源(3.3V)

VSSAIO --- I/O模拟地

VDD3VL --- flash核电源(3.3V),上电后所有时间内都应将该引脚接至3.3V

GPIO和外设共用的管脚

EV-A

PWM1--6

T1PWM_T1CMP --- 定时器1输出

T2PWM_T2CMP --- 定时器2输出

CAP1_QEP1 --- 捕获输入

CAP2_QEP2 --- 捕获输入

CAP3_QEP11 --- 捕获输入

TDIRA --- 计数器方向

TCKINA --- 计数器时钟输入

C1TRIP` --- 比较器1输出

C2TRIP` --- 比较器2输出

C3TRIP` --- 比较器3输出

T1CTRIP`_PDPINTA` --- 定时器1比较输出

T2CTRIP`/EVASOC` --- 定时器2比较输出或EV-A启动外部AD转换输出

EV-B

PWM7--12

T3PWM_T3CMP --- 定时器1输出

T4PWM_T4CMP --- 定时器2输出

CAP4_QEP12 --- 捕获输入

CAP5_QEP4 --- 捕获输入

CAP6_QEP3 --- 捕获输入

TDIRB --- 计数器方向

TCKINB --- 计数器时钟输入

C4TRIP` --- 比较器4输出

C5TRIP` --- 比较器5输出

C6TRIP` --- 比较器6输出

T3CTRIP`_PDPINTB` --- 定时器3比较输出

T4CTRIP`/EVBSOC` --- 定时器4比较输出或EV-B启动外部AD转换输出

中断信号

XINT_XBIO` --- XINT1或XBIO`核心输入

XINT2_ADCSOC --- XINT2或开始AD转换

XINMI_XINT13 --- XNMI或XINT13

SPI

SPISIMOA --- SPI从动输入,主动输出

SPISOMIA --- SPI从动输出,主动输入

SPICLKA --- SPI时钟

SPISTEA --- SPI从动传送使能

SCI-A,SCI-B

SCITXDA --- SCI-A发送

SCIRXDA --- SCI-A接收

SCITXDB --- SCI-B发送

SCIRXDB --- SCI-B接收

CAN

CANTXA --- CAN发送

CANRXA --- CAN接收

MCBSP

MCLKXA --- 发送时钟

MCLKRA --- 接收时钟

MFSXA --- 发送帧同步信号

MSXRA --- 接收帧同步信号

MDXA --- 发送串行数据

MDRA --- 接收串行数据

XF——CPU输出

XF_XPLLDIS` --- 引脚有3个功能:1、XF一通用输出引脚。2、XPLLDIS -- 复位期间此引脚被采样以检查锁相环PLL是否被使能,若该引脚采样为低,PLL将被禁止。此时,不能使用HALT和STANDBY模式。3、GPIO --- 通用输入/输出功能。

我要赚赏金

我要赚赏金