串口通信系列1——接收模块

好久没有写博客了,这次我们谈一谈串口通信,我打算分三遍文章来分析,分别为接收模块、发射模块、接收发送模块。那今天我们就谈一谈uart的接收模块。

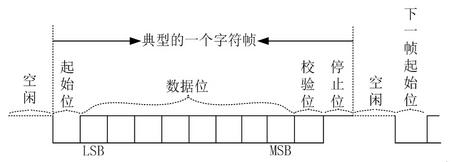

众所周知uart传输数据都是以字符帧格式传输的,如果我们要使用Verilog对uart建模,那我们就必须从很底层去了解它,不像单片机实现串口通信,只需对寄存器配置和查询就行。那么一个字符帧格式到底是怎么构成的?

串口传输数据都是一帧数据(11位),串口总线上高电平是默认状态,当一帧数据开始传输先拉低一位电平,这就是第0位,接下来的8位就是数据位,这是一帧数据中最有意义的八位。接下来的两位是校验证位和停止位,对于接受模块这两位毫无意义。

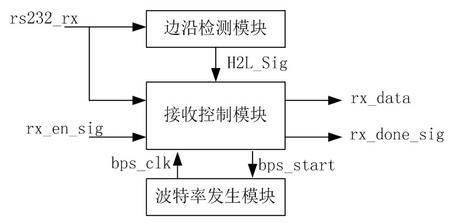

我们已经了解了urat数据以怎样的方式传输,那么接收模块又包含哪些模块?

{C}1.边沿检测模块——检测一帧数据开始的下降沿,检测到下降沿产生一个脉冲信号H2L_Sig给接受控制模块,以表示数据到来,准备接受。

{C}2.波特率发生模块——配置波特率模块,我们以常用的波特率9600bps为例,分析如下:串口一秒钟传输9600bit,一个bit占1/9600s。

{C}3.接受控制模块——当rx_en_sig信号使能,模块对uart发出来的数据进行采集,当采集完一帧数据后就会产生一个rx_done_sig脉冲。

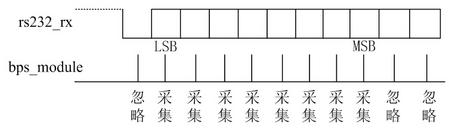

那如何进行采集?

bps_module产生定时在每个位的中间。我的fpga的开发板的晶振是50MHz,也就是说我每记一个数花的时间是1/50000000,一位数据需要记多少个数(波特率使用9600bps)1/9600÷1/50000000=5208,所以当波特率定时模块计数记到2603的时候产生一个脉冲信号bps_clk,让控制模块对rs232_rx信号采集或者忽略。

下面就看看每个模块的代码:

detect_module.v

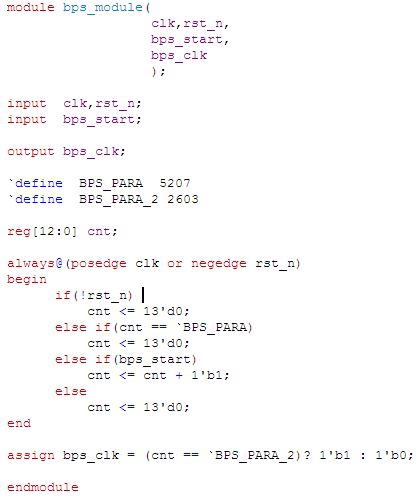

bps_module.v

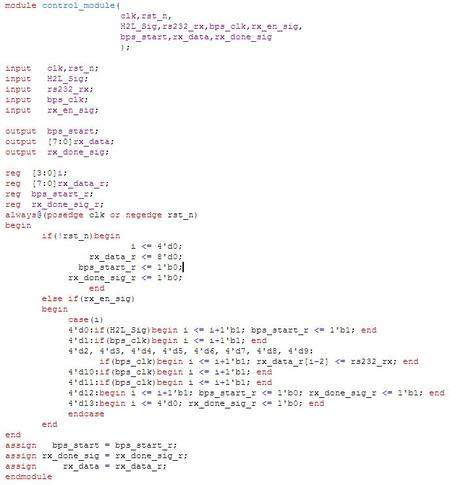

control_module.v

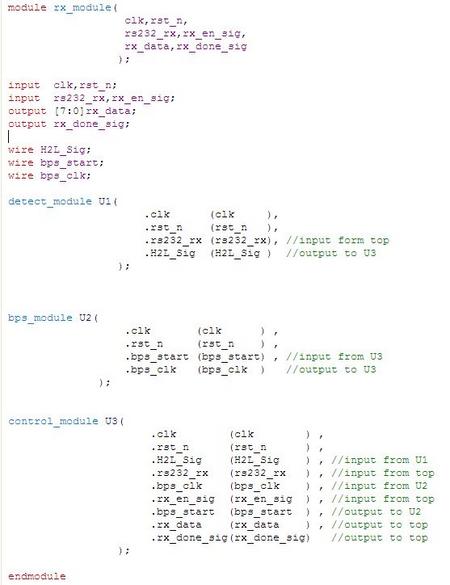

rx_module.v

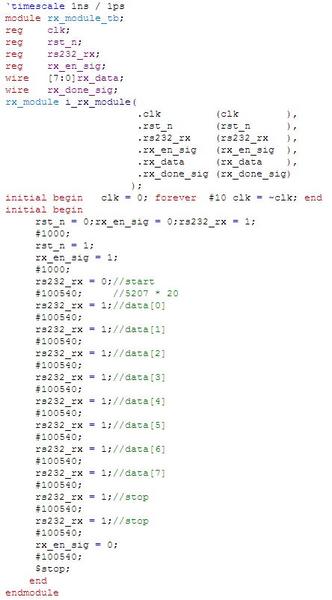

testbench代码:

rx_module_tb.v

modelsim仿真出来的波形:

暂时就写到这儿,欢迎大家交流^_^

(本文转载自博客,作者wiliamzhou)

我要赚赏金

我要赚赏金