EDA技术第4次作业

姓名:李二猛 学号:201405080011 班级:14级电信(专升本)

2014/10/26

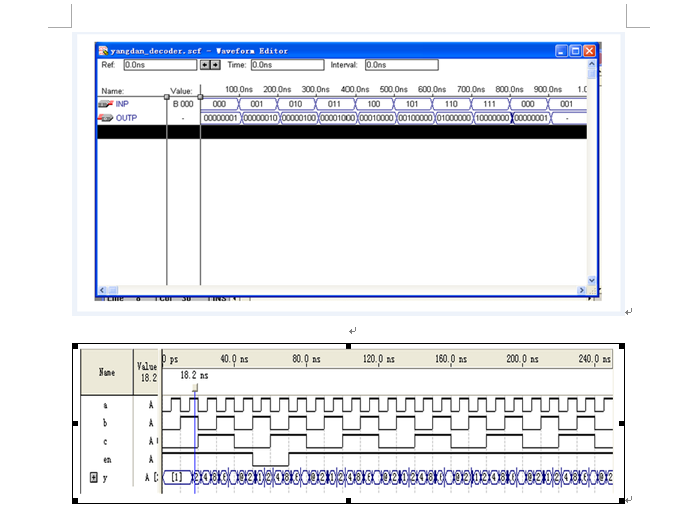

3—3,试分别用IF_THEN语句和CASE语句的表达方式写出此电路的VHDL程序,选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=‟0‟,s0=‟0‟;s1=‟0‟,s0=‟1‟;s1=‟1‟,s0=‟0‟和s1=‟1‟,s0=‟1‟时,分别执行y<=a、y<=b、y<=c、y<=d。

LIBRARY IEEE;

PORT (a,b,c,d: IN STD_LOGIC;

s0: IN STD_LOGIC;

s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END ENTITY mux41;

ARCHITECTURE if_mux41 OF mux41 IS

SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据

BEGIN

s0s1<=s1&s0;

--s1相并s0,即s1与s0并置操作

PROCESS(s0s1,a,b,c,d)

BEGIN

IF s0s1 = "00" THEN y <= a;

ELSIF s0s1 = "01" THEN y <= b

ELSIF s0s1 = "10" THEN y <= c;

ELSE y <= d;

END IF;

END PROCESS;

END ARCHITECTURE if_mux41

--解2:用CASE语句实现4选1多路选择器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux41 IS

PORT (a,b,c,d: IN STD_LOGIC;

s0: IN STD_LOGIC;

s1: IN STD_LOGIC;

y: OUT STD_LOGIC);

END ENTITY mux41;

ARCHITECTURE case_mux41 OF mux41 IS

SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据类型

BEGIN

s0s1<=s1&s0; --s1相并s0,即s1与s0并置操作

PROCESS(s0s1,a,b,c,d)

BEGIN

CASE s0s1 IS --类似于真值表的case语句

WHEN "00" => y <= a;

WHEN "01" => y <= b

WHEN "10" => y <= c

WHEN "11" => y <= d;

WHEN OTHERS =>NULL ;

END CASE;

END PROCESS;

END ARCHITECTURE case_mux41;

3—4,给出1位全减器的VHDL描述;最终实现8位全减器。要求: 1)首先设计1位半减器,然后用例化语句将它们连接起来,图4-20中h_suber是半减器,diff是 输出差(diff=x-y),s_out是借位输出(s_out=1,x<y),sub_in是借位输入。

姓名:李二猛 学号:201405080011 班级:14级电信(专升本)

我要赚赏金

我要赚赏金