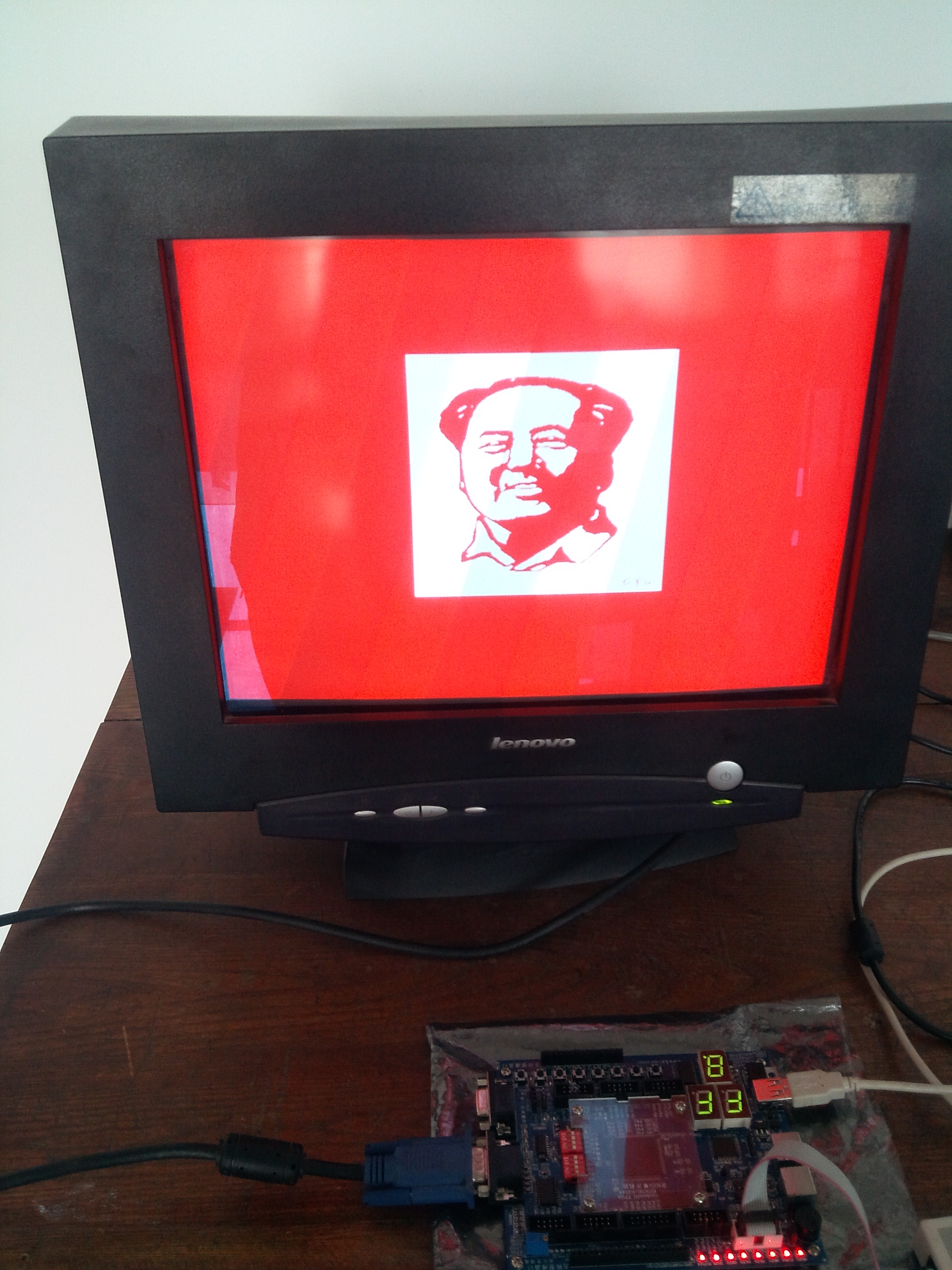

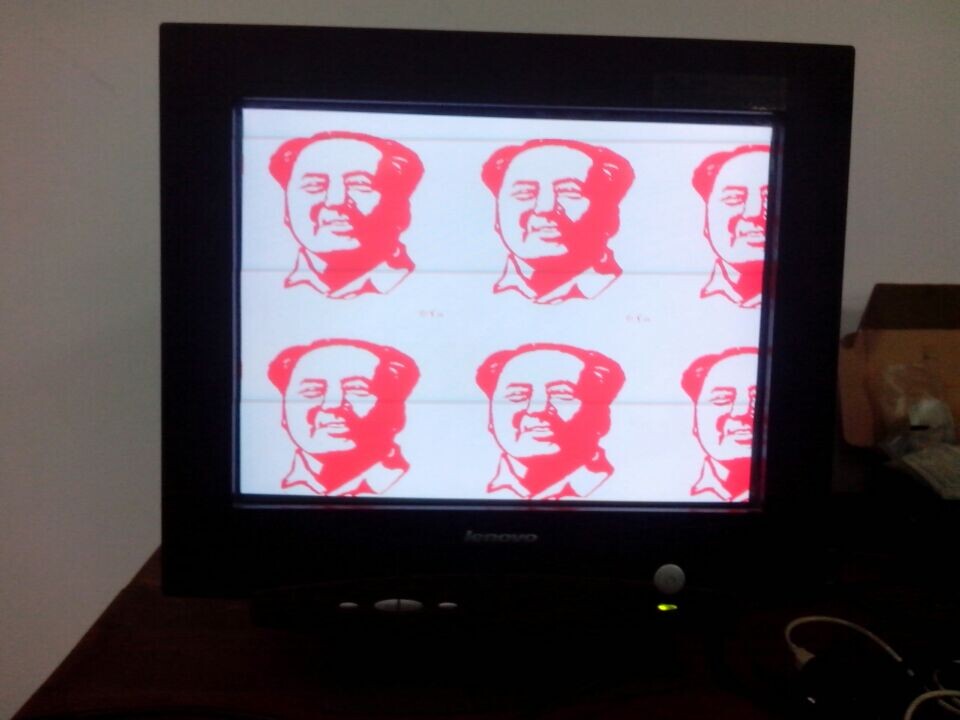

VGA图片显示作业(伟人头像展示)

显示控制信号产生部分。

/******************************************************************************

*Engineer: superdian

*Create Date: 2014/11/26

*Design Name:

*Module Name: vgaV

*Project Name:

*Target Devices: EP3CE5E144C8

*Tool versions:

*Dependencies:

*

*Revision:

*Revision 0.01 - File Created

*Additional Comments:

******************************************************************************/

module vgaV (clk, hs, vs, r, g, b, rgbin, DOUT);//VGA

input clk;

input[2:0] rgbin; //ROM的RGB数据输入

output hs,vs; //行同步信号,厂同步信号

output r,g,b ; //RGB信号输出

output[15:0] DOUT; //ROM地址输出

reg[9:0] hcnt, vcnt;

reg r,g,b;

reg hs,vs;

assign DOUT = {vcnt[7:0]-8'd100, hcnt[7:0]-8'd200} ;//图像在指点像素点开始显示,保证图像显示完全。图片分辨率256*256

always @(posedge clk) //行扫描计数器

begin

if (hcnt<800)

hcnt<=hcnt+1 ;

else

hcnt<={10'b0} ;

end

always @(posedge clk) //厂扫描计数器

begin

if (hcnt==640+8)

begin

if (vcnt<525)

vcnt<=vcnt+1 ;

else

vcnt<={10'b0} ;

end

end

always @(posedge clk) //行同步

begin

if ((hcnt>=656) & (hcnt<752))

hs<=1'b0 ;

else

hs<=1'b1 ;

end

always @(vcnt) //场同步

begin

if ((vcnt>=490) & (vcnt<492))

vs<=1'b0 ;

else vs<=1'b1 ;

end

always @(posedge clk) //显示的内容

begin

if (hcnt<640 & vcnt<480)

if(((hcnt>200)&(hcnt<455))&((vcnt >100)&(vcnt <355)))//指定范围内显示ROM数据

begin

r<=rgbin[2] ; g<=rgbin[1] ; b<=rgbin[0] ;

end

else

begin

r<=1'b1 ; g<=1'b0 ; b<=1'b0 ; //未在指定范围内,显示红色

end

else

begin

r<=1'b0 ; g<=1'b0 ; b<=1'b0 ;

end

end

endmodule

顶层。

/******************************************************************************

*Engineer: superdian

*Create Date: 2014/11/26

*Design Name:

*Module Name: VGAimg

*Project Name:

*Target Devices: EP3CE5E144C8

*Tool versions:

*Dependencies:

*

*Revision:

*Revision 0.01 - File Created

*Additional Comments:

******************************************************************************/

module VGAimg(CLK,HS,VS,R,G,B);

input CLK;

output HS,VS,R,G,B;

wire [2:0] RGBIN;

wire [15:0] ADDRESSIN;

wire CCLK;

clk_pll clk_pll ( //倍频到25MHZ

.inclk0(CLK),

.c0(CCLK)

);

imgROM imgROM (

.address(ADDRESSIN),

.clock(CCLK),

.q(RGBIN)

);

vgaV vgaV(

.clk(CCLK),

.hs(HS),

.vs(VS),

.r(R),

.g(G),

.b(B),

.rgbin(RGBIN),

.DOUT(ADDRESSIN)

);

endmodule

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |