2812具有两个事件管理器模块EVA和EVB,每个EV模块都具有2个通用定时器、3个比较单元、3个捕获单元以及1个正交编码电路。#此前在首页部分显示#

(表格中蓝色的字表示该信号是低电平有效)

通用定时器用来计时的,而且每个定时器还能产生1路独立的PWM波形;

比较单元主要功能就是用来生成PWM波形的,EVA具有3个比较单元,每个单元可以生成一对(两路)互补的PWM波形,生成的6路PWM波形正好可以驱动一个三相桥电路。

捕获单元的功能是捕捉外部输入脉冲波形的上升沿或者下降沿,可以统计脉冲的间隔,也可以统计脉冲的个数。

正交编码电路可以对输入的正交脉冲进行编码和计数,它和光电编码器相连可以获得旋转机械部件的位置和速率等信息。

(1) External compare-output trip inputs—我们可以理解为切断比较输出的外部控制输入,以C1TRIP为例,当比较单元1工作时,其两个引脚PWM1和PWM2正在不断的输出PWM波形,这时候,如果C1TRIP信号变为低电平,则此时PWM1和PWM2引脚被置成高阻态,不会再有PWM波形输出,也就是在这个引脚上输入低电平,则比较输出就会被切断。

(2) External timer-compare trip inputs—我们可以理解为切断定时器比较输出的外部控制输入,以T1PWM_1CMP为例,当定时器1的比较功能在运行,并且T1PWM引脚输出PWM波形的时候,这时候如果T1CTRIP引脚信号变为低电平,则该引脚状态被置成高电平,也不会再有PWM波形输出。

(3) External trip inputs的PDPINTx(x=A或者B)其实是个功率驱动保护,它为系统的安全提供了保护,例如如果当电路中出现电压、电流或者温度急剧上升的时候,如果PDPINTx的中断没有被屏蔽,当PDPINTx的引脚变为低电平时,2812所有的PWM输出引脚都会变为高阻态,从而阻止了电路进一步损坏,达到保护系统的目的。当然PDPINTx在电路设计时就要考虑到给它配一个监视电路状态的信号。

1. 通用定时器---以通用定时器1为例

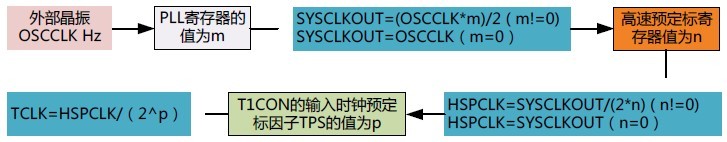

EV事件管理器时钟模块

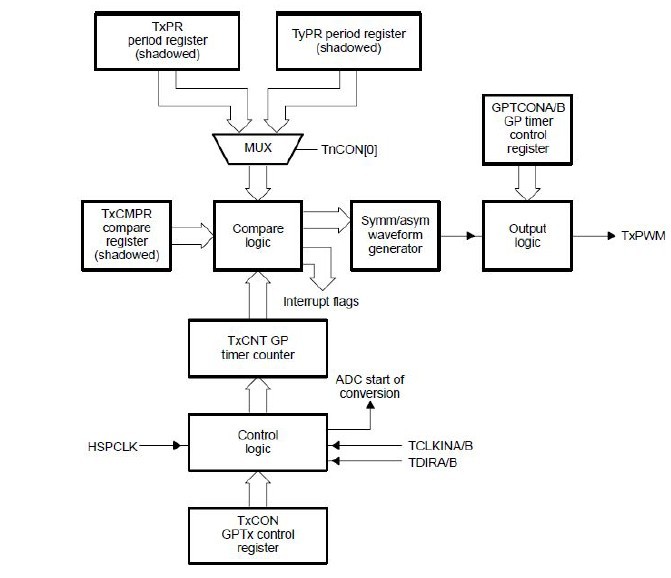

通用定时器模块结构

和T1相关的常用寄存器

T1周期寄存器 ---- T1PR 1 6位

T1比较寄存器 ---- T1CMPR 1 6位

T1计数寄存器 ---- T1CNT 1 6位

T1控制寄存器 ---- T1CON 1 6位

全局定时器控制寄存器A ---- GPTCONA 1 6位

T1的常见输入信号

来自于CPU的内部时钟

外部时钟输入TCLKINA,最大频率为器件自身时钟的1/4,也就是1/4*150M

TDIRA/B,用于定时器的增/减计数模式

复位信号RESET

T1的输出信号

定时器的比较输出T1PWM_T1CMP

送给ADC模块的AD转换启动信号

下溢、上溢、比较匹配和周期匹配信号

计数方向指示

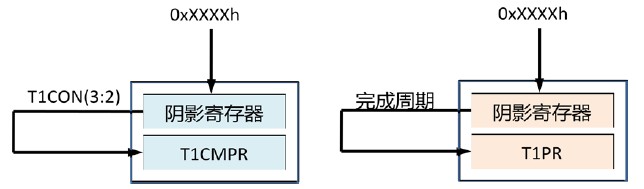

阴影寄存器作用---重载条件

可以在一个周期的任何时刻向T1CMPR或者T1PR写入新的数值,假设我们要向T1CMPR写入新的数值0xXXXXh,首先将这个数值写入T1CMPR的阴影寄存器,当T1CON中第3位TCLD1和第2位TCLD0所指定的特定事件发生时,阴影寄存器的数据就会被写入T1CMPR的工作寄存器。

向T1PR写入新的数据0xXXXXh,数据也会被立即写入阴影寄存器,只有当T1CNT的完成这个周期的计数,值为0的时候,阴影寄存器中的内容才会被载入到工作寄存器中,从而改变T1PR的值。

定时器比较寄存器重载条件

TCLD1 TCLD0

0 0 当计数器T1CNT值为0

0 1 当计数器T1CNT值为0或者等于周期寄存器

1 0 立即载入

1 1 保留

定时器的计数方式---由T1CON第12位·11位决定

TMODE1 TMODE0

0 0 停止/保持

0 1 连续增/减模式

1 0 连续增模式

1 1 定向增/减计数模式(directional up/down count mode)

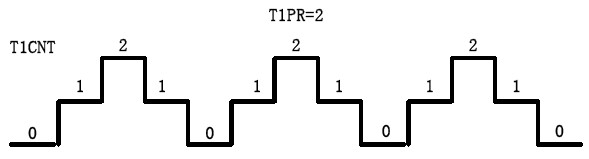

连续增/减技术模式-----实际的计数周期为2*T1PR

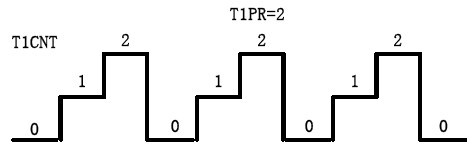

连续增模式-----实际的计数周期为T1PR+1

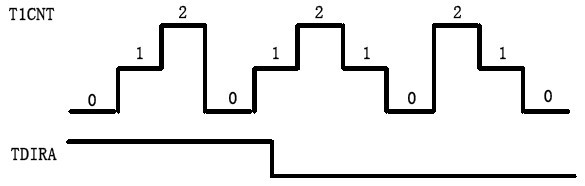

定向增或者减计数模式

T1CNT进行增计数或者是减计数,取决于引脚TDIRA的电平, 如果TDIRA为高电平,则T1CNT进行增计数;如果TDIRA为低电平,则T1CNT进行减计数。如果是在计数过程中TDIRA电平发生了变化,那么必须在完成当前计数周期后的下一个CPU时钟周期时,计数方向发生改变。

T1相关的中断

上溢中断T1OFINT、下溢中断T1UFINT、比较中断T1CINT、周期中断T1PINT

(1)当T1CNT的值为0xFFFFh的时候,发生定时器T1的上溢中断。当上溢事件发生后,再过1个CPU时钟周期,则上溢中断的标志位被置位。

(2)当T1CNT的值为0x0000h的时候,发生定时器T1的下溢中断。当下溢事件发生后,再过1个CPU时钟周期,则下溢中断的标志位被置位。

(3)当T1CNT的值和T1比较寄存器T1CMPR的值相等时,发生定时器T1的比较中断。当发生比较匹配时,再过1个CPU时钟周期,则比较中断的标志位被置位。

(4)当T1CNT的值和T1周期寄存器T1PR的值相等时,发生定时器T1的周期中断。当发生周期事件时,再过1个CPU时钟周期,则周期中断的标志位被置位。

当某个中断的标志位被置位,如果该中断已经使能,则会像PIE模块发送中断申请。退出中断的时候,一定要手动清除外设中断标志位。在EV中,和上述中断相关的寄存器是EVAIFRA、EVAIMRA 、EVAIFRB、EVAIMRB

上述事件除了能够产生中断以外,还能产生一个ADSOC信号,就是启动AD转换的信号,这样可以周期性的去启动AD转换。依据寄存器GPTCONA的第8和第7位,这个功能的优点就在于允许在CPU不干涉的情况下使通用定时器的事件和ADC启动转换同步进行

GPTCONA中T1启动AD转换的信号的相关位(T1TOADC)

Bit8 bit7

0 0 不启动ADC

0 1 下溢中断启动ADC

1 0 周期中断启动ADC

1 1 比较中断启动ADC

定时器的同步

T2可以使用T1的周期寄存器而忽略自身的周期寄存器,也可以使用T1的使能位来启动T2计数,这样的功能保证了T1和T2能够实现同步计数

1.将T2CON的T2SWT1置1,实现由T1CON的TENABLE位来启动通用定时器2的计数,这样,两个计数器(T1、T2)就能同时启动计数。

2.对T1CNT和T2CNT进行不同值的初始化。

3.将T2CON的SELT1PR置1,指定定时器2将定时器1的周期寄存器作为自己的周期寄存器。

我要赚赏金

我要赚赏金