今天收到了ZYNQ 7000开发板,谢谢EEPW和V3学院。

首先是个大家伙,身价很高

打开发现里边还有一层

再打开,是装静电塑料装的板子和仿真器还有若干连线

照个全家福

这下好了,有的学了。以后继续分享

【Zynq7000系列开发手记】+装机测试

根据EagleGoSDSOC 快速入门教材

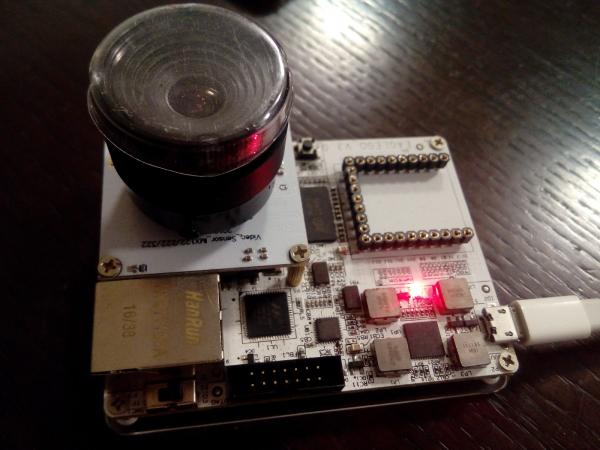

第一步,检查板卡是否正常,没有问题之后连接供电

1.使用下载电缆可以对 FPGA 进行调试和 flash 固化。下载电缆一端通过 USB-A 电缆连接到 PC,另一

端通过 14pin jtag 接口连接到板卡的下载接口。

2.设置启动方式跳线和给板卡供电,

第二步,添加 platform

1.将例程 sdsoc 里面的 platform 目录下的 snowleo2 复制到 sdsoc2015.4 的安装目录下的 platform 目录里

面 。

第三步,打开 IDE SDSOC2016.1 新建 sdsoc project

1.File --> NEW --> SDSOC PROJECT,选择相应的 platform。

2.接下来可以在 src 目录下根据自己的需求也可以直接将公司提供的工程直接添加进目录。

第四步,编译软件工程

4.1 为了体现 sdsoc 的特点,我们拿 ip 加速之前和 ip 加速之后做一下对比,首先只编译软件工程

选择 debug,其他默认, 然后编译工程 右键单击工程->build project 或者 ctrl+b。

第五步,选择部分 ip 进行加速。

1.打开 project.sdsoc 文件 选择编译后产生相应的选项如图所示,为了稳定选择 100M 的时钟,

选择 Generate SD Card Image 当编译结束后会在该目录生成相应的镜像文件,可以直接将这些文件

放入 tf 卡,上电启动即可 。

2.点击添加按钮,选择想要加速的 ip,可以多选

第六步,编译。

1.编译步骤同第一次编译,编译时间与 PC 的性能有关,通常在 30~50 分钟左右。编译完之后会产

生 bit 和 elf 等文件。

第七步,运行。

1.右击工程名 --> RUNAS --> run configuration..

2.选择相应的 bit 文件。如图 7.1

3.选择相应的 elf 文件, Apply --> RUN 如下图

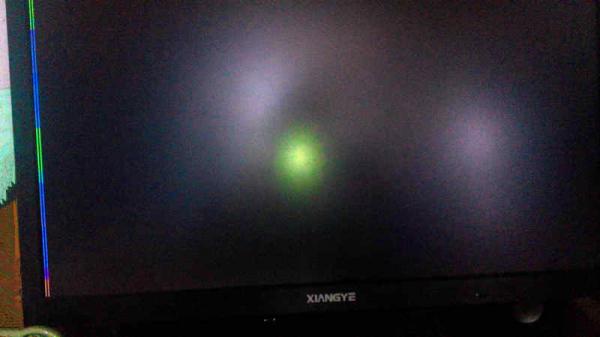

图像模糊还需排查问题

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |