小弟最近写了一个带收发FIFO的UART程序。UART是一种通用串行数据总线,用于异步通信,可以实现全双工发送和接收,作为很多FPGA教材入门性的实验,可以说大家都比较很熟悉了,但是网上大部分的uart程序中都不带FIFO,那么为什么小弟要加FIFO呢。于是小弟就想利用手头上EasyFPGA060开发板编写出带收发FIFO的UART。

经过了将近一周的设计与调试之后,我的串口程序新鲜出炉啦。在程序中,我设置一帧数据为11位组成(一位起始位+八位数据位+两位终止位),如果需要保证传输的数据更稳定,可以将终止位的第一位改成奇偶校验位;如果希望传输速度更快,可以将终止位改成一位,这样有效位的传输效率更高(从8/11提高到8/10),在波特率不变的情况下,能传输更多的有效位数,从而提高了传输的速率。通过调试,程序在115200bps情况下能实现连续传输(我的串口调试助手最高只能设置115200bps,如果需要更高的波特率,请自行根据程序中的注解更改参数设置)。

下面介绍程序的模块图、仿照测试结果以及实际调试结果:

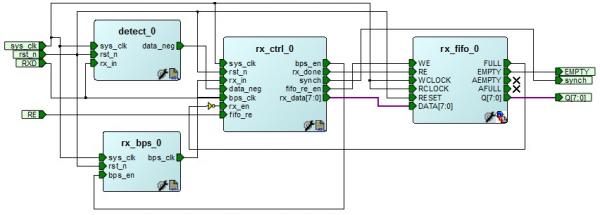

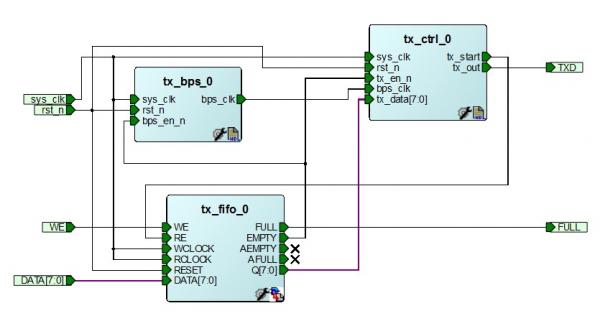

程序主要由如图1所示的接收部分和如图2所示发送部分两块组成:

模块图是在Libero SoC v11.3 中的SmartDesign来设计的顶层文件。其中利用的FIFO都是使用Libero中的IP核来设计的。具体的模块功能在程序中有详细描述,有兴趣的同学可以自行阅读程序。

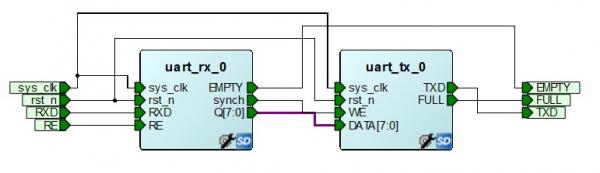

为了更形象的体现设计的正确性,我还做了自发自收模块,通过这种模式在串口调试助手中验证设计的正确性。自发自收的模块图如图3所示:

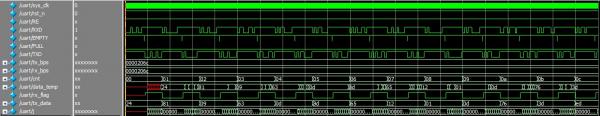

我仿照特权同学在《****玩转FPGA》这本书中对串口程序写的测试脚本,对程序进行了仿真测试:将一个8位随机的信号加工成一帧(11位)信号,经过并转串之后输入到模块的RXD端,之后测试TXD端输出的信号是否和传输的一致。其ModelSim仿真波形图如图4所示:

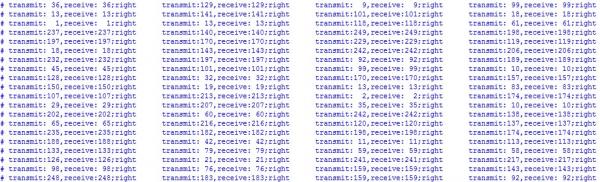

图4中的倒数第二行是发送的数据,而倒数第四行是接收到的信号,可以看到,系统在接受信号后准确的通过11位数据再传输出去。整个程序很好的完成了自发自收的功能。仿真中我还通过$write来显示当前的发送数据与接收数据,当收和发的数据一致时候,后面写上right,否则,则显示wrong。仿真输出如图5所示:

仿真成功之后,我们就可以把程序下载到板子上试试效果啦:

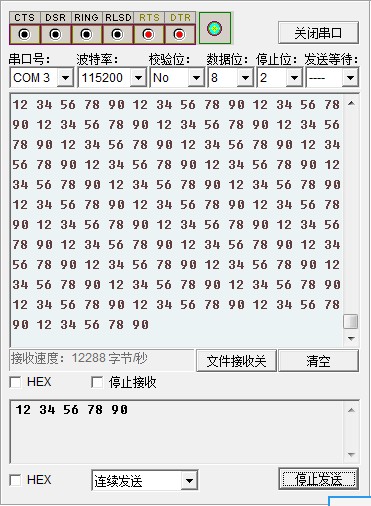

这里设置RXD和TXD分别为21与20管脚,需要更改的请在I/O Attributes里面自行设置。图6下方的板子是USB转串口模块,大家可以根据实际自行更换。通过串口调试助手,我们可以看到如图7所示程序能在115200bps情况下连续发送而不出错。

需要注意的是,在传送的时候,要设置波特率位115200,数据位为8位,停止位为2位。在这种条件下,才能保证程序与串口调试助手收发正常。

以上,就是小弟所以的内容展示,如果有错误,请大家及时指出。最后希望以后和大家在这个平台里共同学习,共同进步~

转发在周立功单片机

我要赚赏金

我要赚赏金