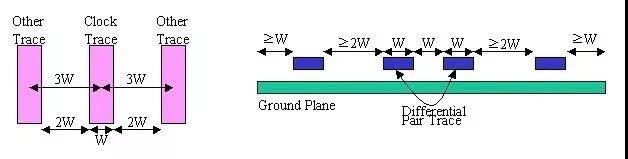

在PCB设计中,对于强干扰信号线和对干扰很敏感的信号线产生的串扰,会存在于走线之间,这种不良影响不仅与时钟或周期信号有关,而且也会对系统中其他的重要走线,数据线、地址线、控制线和IO产生影响。为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,这称为3W规则。(如要达到98%的电场不互相干扰,可使用10W的间距。)

3W原则的成立条件

3W原则虽然容易记,但要强调一点,这个原则成立是有先前条件的。从串扰成因的物理意义考量,要有效防止串扰,该间距与叠层高度、导线线宽相关。

对于四层板,走线与参考平面高度距离(5~10mils),3W是够了;但兩层板,走线与参考层高度距离(45~55mils),3W对高速信号走线可能不够。

3W原则一般是在50欧姆特征阻抗传输线条件下成立。

3W原则不能完全避免串扰

3W原则是一种防止串扰的一种方法,但此方法仅作为一种参考,并作为理解如何防止串扰的一种启发。在实际PCB设计中,3W原则并不能完全满足避免串扰的要求。按实践经验,如果没有屏蔽地线的话,印制信号线之间大于lcm以上的距离才能很好地防止串扰。因此,在PCB线路布线时,就需要在噪声源信号(如时钟走线)与非噪声源信号线之间,及受EFTlB、ESD等干扰的“脏“线与需要保护的“干净”线之间,不但要强制使用3W原则,而且还要进行屏蔽地线包地处理,以防止串扰的发生。此外,不是所有PCB上的走线都必须遵循3W布线原则。使用这一设计指导原则,在PCB布线前,决定哪些条走线必须使用3W原则是十分重要的。

最后总结一点:3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。

(以上内容整理自网络,版权归原作者所有,如有侵权请联系删除。)

我要赚赏金

我要赚赏金