7.1电源管理概述

处理器广泛地利用门时钟来禁能那些未用的功能和未用功能块的输入,因此只有正在有效使用中的逻辑才会消耗动态功率。

ARMv7-M架构支持为减少功耗而让Cortex-M3和系统时钟停止运行的系统睡眠模式。

7.2系统电源管理

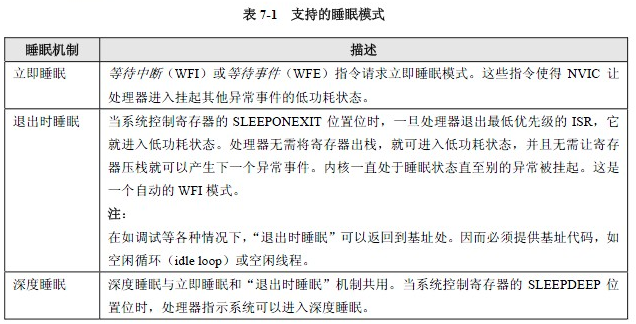

对系统控制寄存器进行写操作(见“系统控制寄存器”)可以控制Cortex-M3系统功耗的状态,表7-1列出了支持的睡眠模式。

a.即使没有异常被激活也可以执行WFI指令。不要使用WFI指令来探测异常是否发生。WFI通常使用

在线程模式下的空闲循环中。要了解更多有关WFI、WFE、BASEPRI以及PRIMASK的信息,请参考

“ARMv7-M架构参考指南”。

处理器导出以下信号以指示处理器进入睡眠的具体时间:

SLEEPING该信号在立即睡眠或“退出时睡眠”模式下有效,表示处理器时钟可以停

止运行。在接收到一个新的中断后,NVIC会使该信号变无效,使内核退出睡眠。有关

SLEEPING的用法实例见“SLEEPING”。

SLEEPDEEP当系统控制寄存器的SLEEPDEEP位置位时,该信号在立即睡眠或“退

出时睡眠”模式下有效。该信号被传送给时钟管理器,并可以用来门控处理器和包含锁相环

(PLL)的系统元件以节省功耗。在接收到新的中断时,嵌套向量中断控制器(NVIC)将

SLEEPDEEP信号变无效,并在时钟管理器显示时钟稳定时让内核退出睡眠。有关

SLEEPDEEP的用法实例见“SLEEPDEEP”。

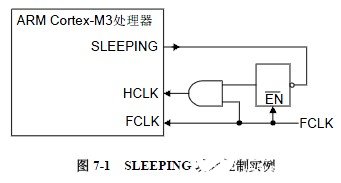

7.2.1 SLEEPING

图7-1给出了如何在低功耗状态利用SLEEPING来门控处理器的HCLK时钟以减少功

耗的实例。如有必要,还可以使用SLEEPING来门控其他系统元件。

为了探测中断,处理器必须一直接收自由振荡的FCLK。FCLK用于对以下元件计时:

B)探测中断的NVIC中的少量逻辑电路

B)DWT和ITM模块。这些模块被使能相应功能后可以在睡眠期间产生跟踪包。如果

“调试异常与监控寄存器”的TRCENA位使能,那些模块的功耗将会降低。见“调

试异常与监控寄存器”。

在SLEEPING信号有效期间可以降低FCLK频率。

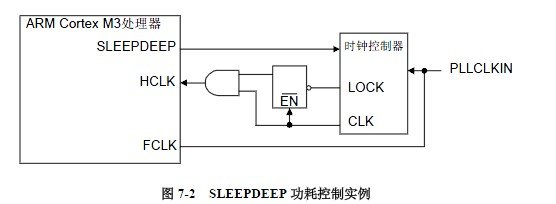

7.2.2 SLEEPDEEP

图7-2给出了如何在低功耗状态利用SLEEPDEEP来停止时钟控制器以进一步减少功耗

的实例。退出低功耗状态时,LOCK信号指示PLL稳定,并且此时使能Cortex-M3时钟是

安全的,这可以保证处理器不会重启直至时钟稳定。

为了检测中断,处理器在低功耗状态下必须接收自由振荡的FCLK。在SLEEPDEEP有效期

间可以降低FCLK频率。

《STM32中文参考手册_V10.pdf》

4.1电源

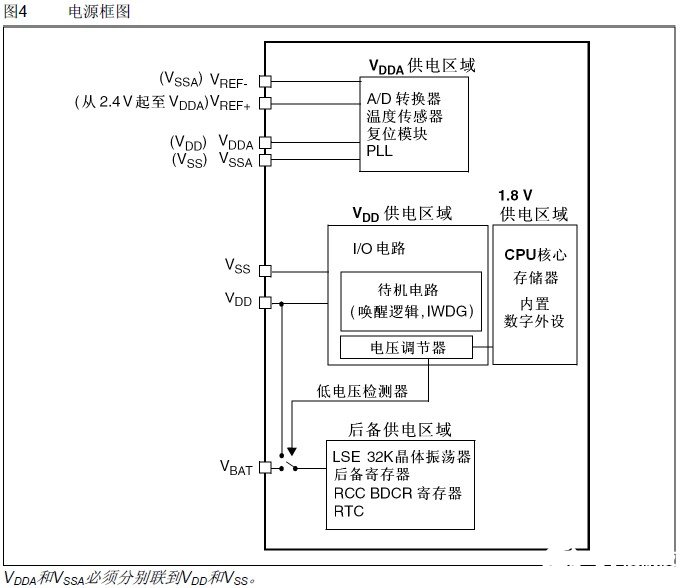

STM32的工作电压(VDD)为2.0~3.6V。通过内置的电压调节器提供所需的1.8V电源。 当主电源VDD掉电后,通过VBAT脚为实时时钟(RTC)和备份寄存器提供电源。

4.1.2电池备份区域使用电池或其他电源连接到VBAT脚上,当VDD断电时,可以保存备份寄存器的内容和维持RTC的功能。VBAT脚也为RTC、LSE振荡器和PC13至PC15供电,这保证当主要电源被切断时RTC能继续工作。切换到VBAT供电由复位模块中的掉电复位功能控制。 如果应用中没有使用外部电池,VBAT必须连接到VDD引脚上。

如果在应用中没有外部电池,建议VBAT在外部通过一个100nF的陶瓷电容与VDD相连

4.1.3电压调节器

复位后调节器总是使能的。根据应用方式它以3种不同的模式工作。 ● 运转模式:调节器以正常功耗模式提供1.8V电源(内核,内存和外设)。

● 停止模式:调节器以低功耗模式提供1.8V电源,以保存寄存器和SRAM的内容。

● 待机模式:调节器停止供电。除了备用电路和备份域外,寄存器和SRAM的内容全部丢失。

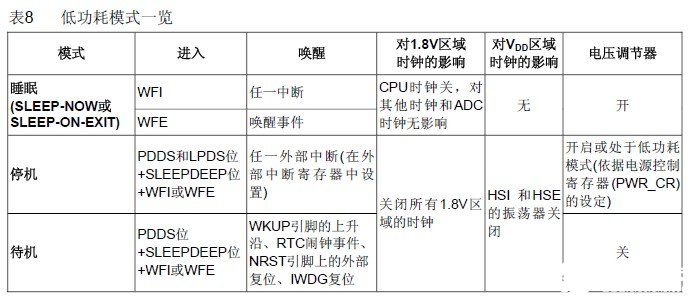

4.3低功耗模式

在系统或电源复位以后,微控制器处于运行状态。当CPU不需继续运行时,可以利用多种低功耗模式来节省功耗,例如等待某个外部事件时。用户需要根据最低电源消耗、最快速启动时间和可用的唤醒源等条件,选定一个最佳的低功耗模式。STM32F10xxx有三种低功耗模式:

● 睡眠模式(Cortex?-M3内核停止,所有外设包括Cortex-M3核心的外设,如NVIC、系统时钟(SysTick)等仍在运行)

●停止模式(所有的时钟都已停止)

● 待机模式(1.8V电源关闭)

此外,在运行模式下,可以通过以下方式中的一种降低功耗:

● 降低系统时钟

●关闭APB和AHB总线上未被使用的外设时钟。

4.3.1降低系统时钟

在运行模式下,通过对预分频寄存器进行编程,可以降低任意一个系统时钟(SYSCLK、HCLK、PCLK1、PCLK2)的速度。进入睡眠模式前,也可以利用预分频器来降低外设的时钟。详见第6.3.2节:时钟配置寄存器(RCC_CFGR)。

4.3.2外部时钟的控制

在运行模式下,任何时候都可以通过停止为外设和内存提供时钟(HCLK和PCLKx)来减少功耗。 为了在睡眠模式下更多地减少功耗,可在执行WFI或WFE指令前关闭所有外设的时钟。 通过设置AHB外设时钟使能寄存器(RCC_AHBENR)、APB2外设时钟使能寄存器(RCC_APB2ENR)和APB1外设时钟使能寄存器(RCC_APB1ENR)来开关各个外设模块的时钟。

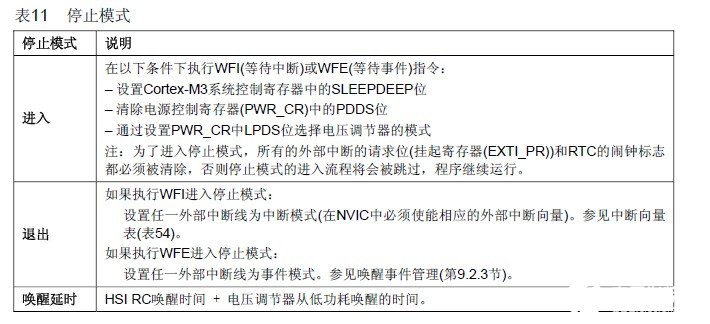

4.3.4停止模式

停止模式是在Cortex?-M3的深睡眠模式基础上结合了外设的时钟控制机制,在停止模式下电压调节器可运行在正常或低功耗模式。此时在1.8V供电区域的的所有时钟都被停止,PLL、HSI和HSE RC振荡器的功能被禁止,SRAM和寄存器内容被保留下来。在停止模式下,所有的I/O引脚都保持它们在运行模式时的状态。进入停止模式关于如何进入停止模式,详见表11。在停止模式下,通过设置电源控制寄存器(PWR_CR)的LPDS位使内部调节器进入低功耗模式,能够降低更多的功耗。 如果正在进行闪存编程,直到对内存访问完成,系统才进入停止模式。 如果正在进行对APB的访问,直到对APB访问完成,系统才进入停止模式。 可以通过对独立的控制位进行编程,可选择以下功能:

●独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了独立看门狗,除了系统复位,它不能再被停止。详见17.3节。

●实时时钟(RTC):通过备份域控制寄存器(RCC_BDCR)的RTCEN位来设置。

●内部RC振荡器(LSI RC):通过控制/状态寄存器(RCC_CSR)的LSION位来设置。

●外部32.768kHz振荡器(LSE):通过备份域控制寄存器(RCC_BDCR)的LSEON位设置。

在停止模式下,如果在进入该模式前ADC和DAC没有被关闭,那么这些外设仍然消耗电流。通过设置寄存器ADC_CR2的ADON位和寄存器DAC_CR的ENx位为0可关闭这2个外设。退出停止模式关于如何退出停止模式,详见下表。当一个中断或唤醒事件导致退出停止模式时,HSI RC振荡器被选为系统时钟。当电压调节器处于低功耗模式下,当系统从停止模式退出时,将会有一段额外的启动延时。如果在停止模式期间保持内部调节器开启,则退出启动时间会缩短,但相应的功耗会增加。

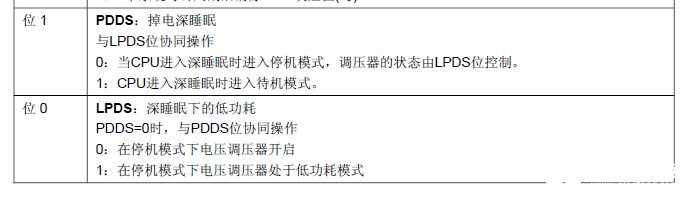

其中对PWR_CR的PDDS和LPDS的配置:

//进入停止模式

{

//的LPDS并清除PWR_CR的PDDS

u32 tmpreg tmpreg = PWR-》CR;

tmpreg &= ~(1《《1); //清除PWR_CR的PDDS

tmpreg “=(1《《0); //设置PWR_CR的LPDS

PWR-》CR = tmpreg;

SCB-》SCR|=1《《2; //使能SLEEPDEEP位(SYS-》CTRL)

WFI_SET(); //执行WFI指令

}

其中THUMB指令不支持汇编内联,采用如下方法实现执行汇编指令WFI

__asm void __inline WFI_SET(void)

{

WFI;

}

4.3.5待机模式

待机模式可实现系统的最低功耗。该模式是在Cortex-M3深睡眠模式时关闭电压调节器。整个1.8V供电区域被断电。PLL、HSI和HSE振荡器也被断电。SRAM和寄存器内容丢失。只有备份的寄存器和待机电路维持供电。

进入待机模式

关于如何进入待机模式,详见表12。 可以通过设置独立的控制位,选择以下待机模式的功能:

● 独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了独立看门狗,除了系统复位,它不能再被停止。

● 实时时钟(RTC):通过备用区域控制寄存器(RCC_BDCR)的RTCEN位来设置。

● 内部RC振荡器(LSI RC):通过控制/状态寄存器(RCC_CSR)的LSION位来设置。

● 外部32.768kHz振荡器(LSE):通过备用区域控制寄存器(RCC_BDCR)的LSEON位设置。 退出待机模式。

当一个外部复位(NRST引脚)、IWDG复位、WKUP引脚上的上升沿或RTC闹钟事件的上升沿发生时,微控制器从待机模式退出。从待机唤醒后,除了电源控制/状态寄存器(PWR_CSR)(见第4.4.2节),所有寄存器被复位。

我要赚赏金

我要赚赏金